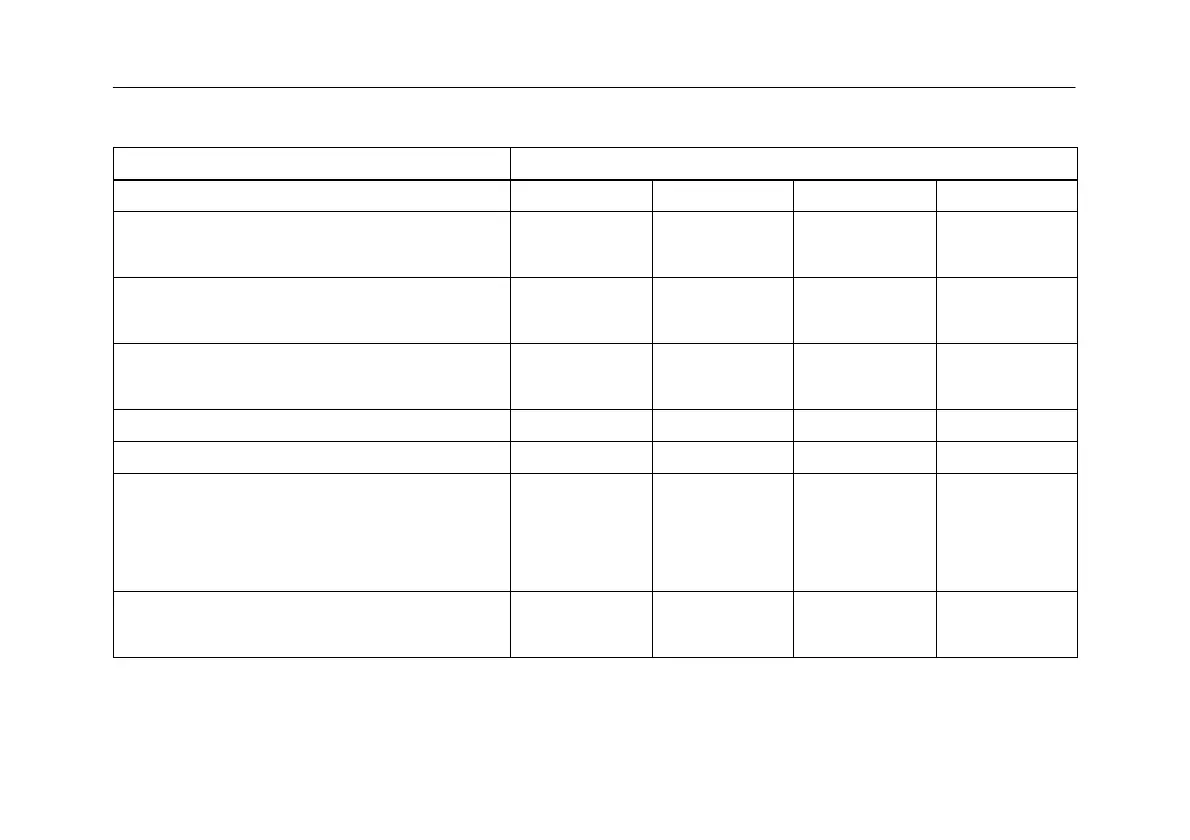

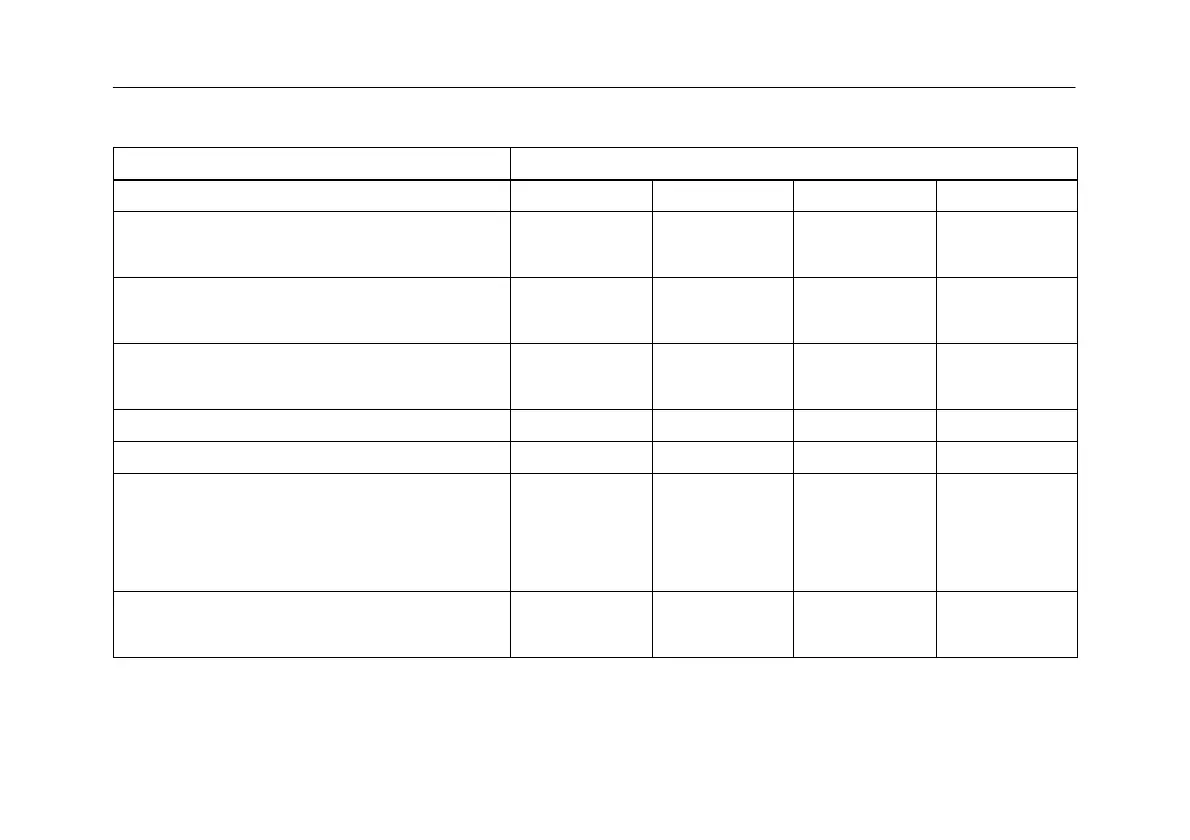

Execution Times with Indirect Addressing1

20

S7-400 Instruction List

A5E00267845-01

The execution time for loading the address of the instruction from the various areas is shown in the following table.

Address is in ... Execution Time in s

CPU 412 CPU 414 CPU 416 CPU 417

Bit memory area M

Word

Double word

0.2

0.2

0.12

0.12

0.08

0.08

0.06

0.06

Data block DB/DX

Word

Double word

0.3

0.3

0.18

0.18

0.12

0.12

0.12

0.12

Local data area L

Word

Double word

0.2

0.2

0.12

0.12

0.08

0.08

0.06

0.06

AR1/AR2 (area-internal) 0.0 * 0.0 * 0.0 * 0.0 *

AR1/AR2 (area-crossing) 0.0 * 0.0 * 0.0 * 0.0 *

Parameter (word) ... for:

S Timers

S Counters

S Block calls

0.4

0.4

0.4

0.24

0.24

0.24

0.16

0.16

0.16

0.15

0.15

0.15

Parameter (double word) ... for

Bits, bytes, words

and double words

0.4 0.24 0.16 0.15

* Address registers AR1/AR2 do not need to be loaded in separate cycles for addressing.

The pages that follow contain examples for calculating the instruction run time for the various indirectly addressed instructions.

Loading...

Loading...