Load and Transfer Instructions for Address Registers

57

S7-400 Instruction List

A5E00267845-01

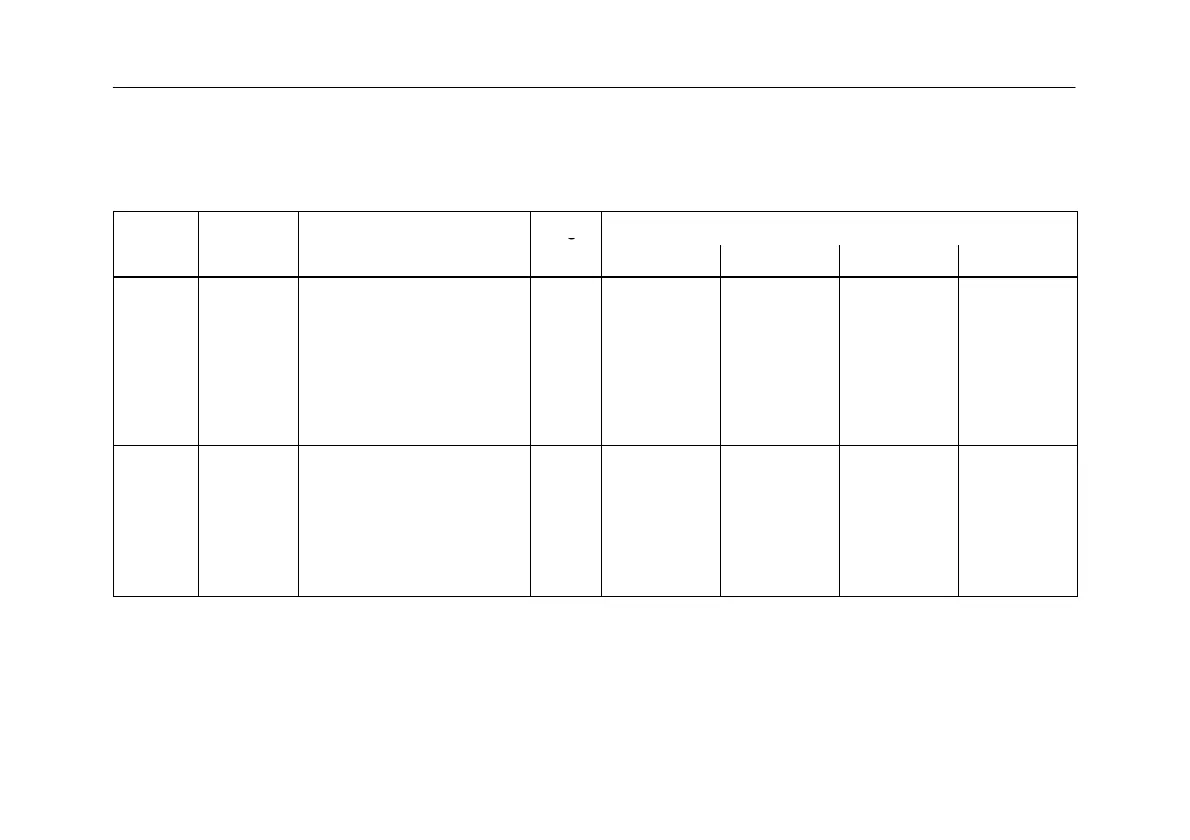

Load and Transfer Instructions for Address Registers

Loading a double word from a memory area or register into address register 1 (AR1) or address register 2 (AR2). The status word is not

affected.

Length

Execution Time in s

tion

ID

Words

CPU 412 CPU 414 CPU 416 CPU 417

LAR1

–

AR2

DBD a

DID a

m

LD a

MD a

Load contents from ...

ACCU1

Address register 2

Data double word

Instance data double word

32-bit constant as pointer

Local data double word

Bit memory double word

... into AR1

1

1

2

2

3

2

2

0.2

0.2

0.3

0.3

0.2

0.2

0.2

0.12

0.12

0.18

0.18

0.12

0.12

0.12

0.08

0.08

0.12

0.12

0.08

0.08

0.08

0.06

0.06

0.12

0.12

0.062

006

006

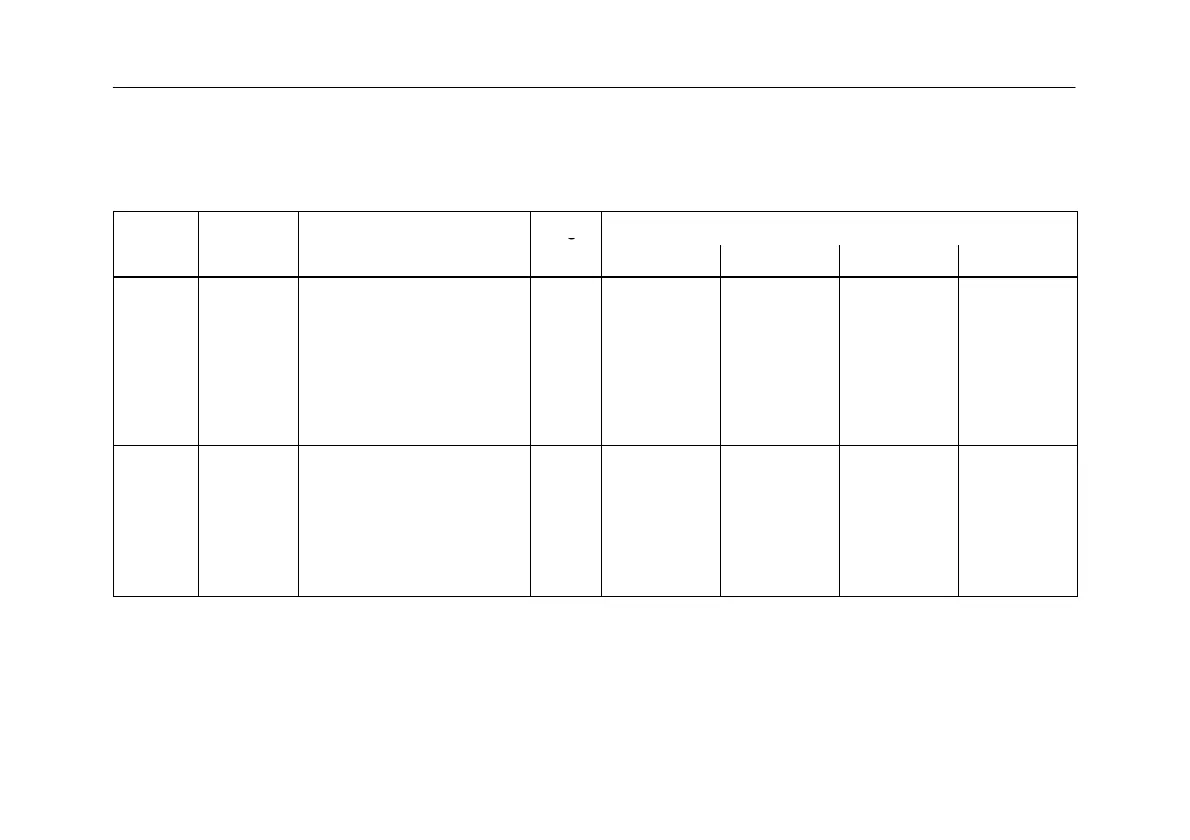

LAR2

–

DBD a

DID a

m

LD a

MD a

Load contents from ...

ACCU1

Data double word

Instance data double word

32-bit constant as pointer

Local data double word

Bit memory double word

... into AR2

1

2

2

3

2

2

0.2

0.3

0.3

0.2

0.2

0.2

0.12

0.18

0.18

0.12

0.12

0.12

0.08

0.12

0.12

0.08

0.08

0.08

0.06

0.12

0.12

0.062

0.06

0.06

Loading...

Loading...