– 17 –

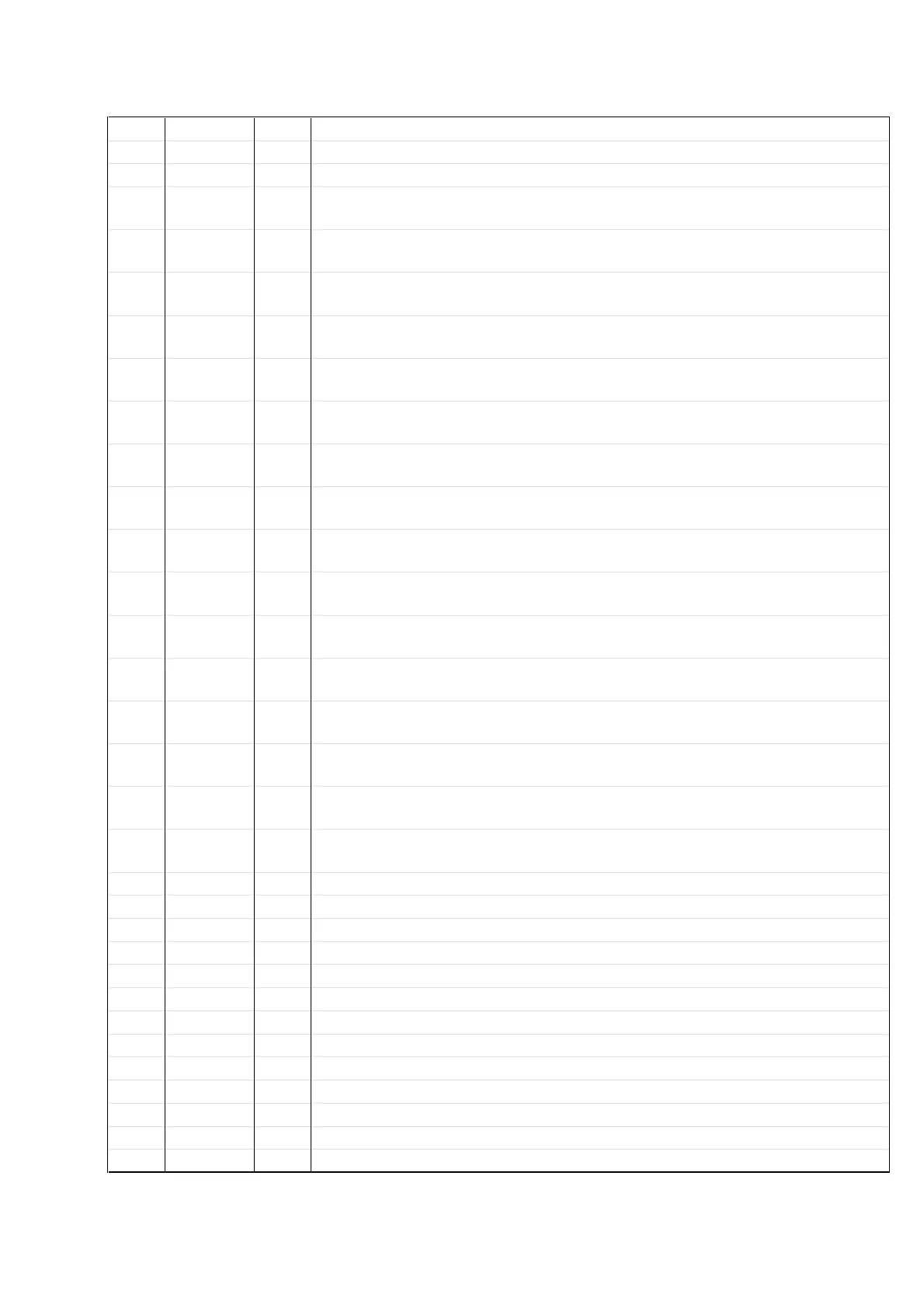

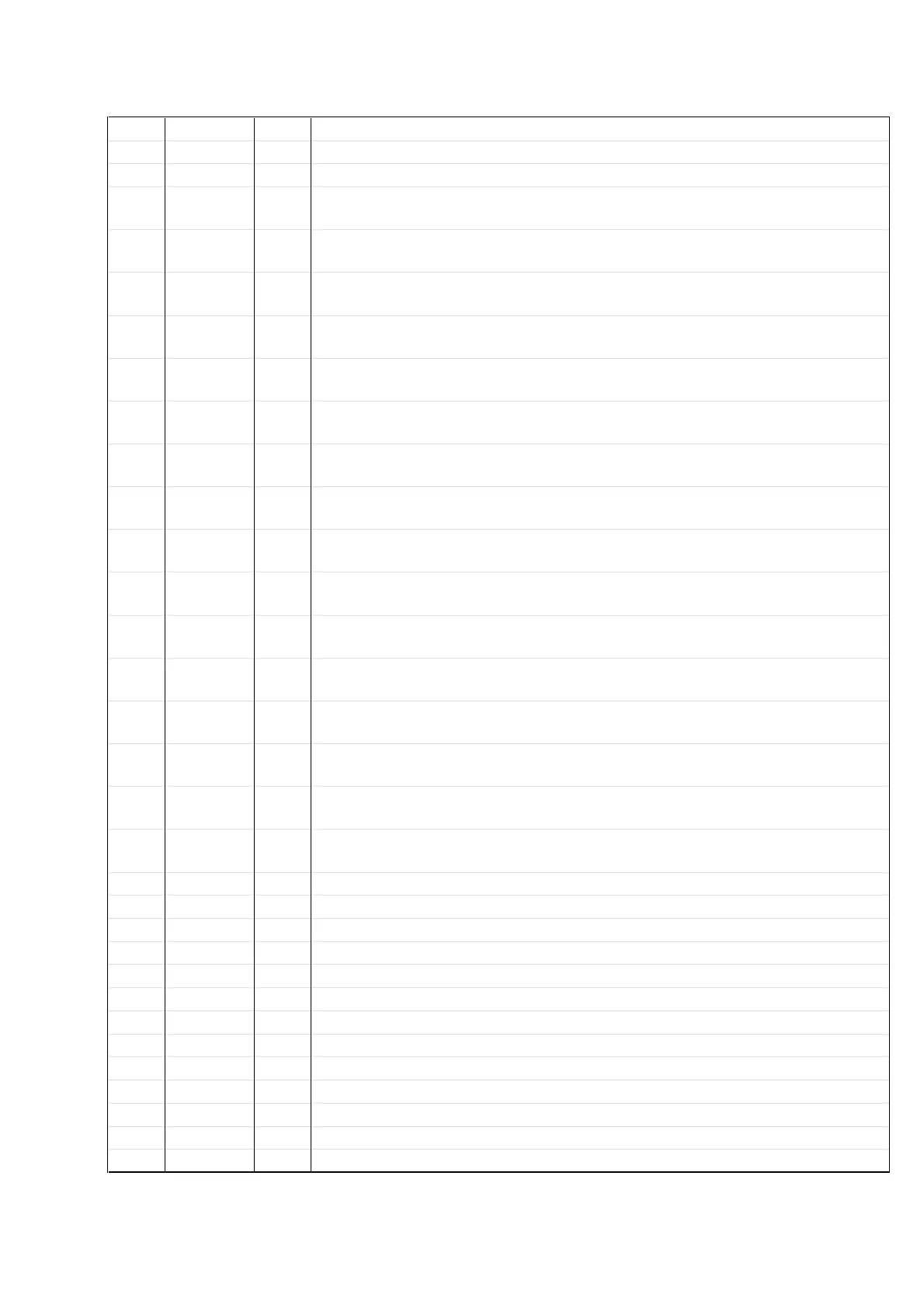

Pin No. Pin Name I/O Function

44 WDCK O Word clock signal (88.2 kHz) output terminal Not used (open)

45 LRCK O L/R sampling clock signal (44.1 kHz) output to the CXD8595Q (IC301)

46 DATA O

DA16 output when PSSL=“H”, 48-bit slot serial data output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Serial data output to the CXD8595Q (IC301)

47 BCLK O

DA15 output when PSSL=“H”, 48-bit slot bit clock signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Bit clock signal (2.8224 MHz) output to the CXD8595Q (IC301)

48 64 DATA O

DA14 output when PSSL=“H”, 64-bit slot serial data output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Not used (open)

49 64 BCLK O

DA13 output when PSSL=“H”, 64-bit slot bit clock signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Not used (open)

50 64 LRCK O

DA12 output when PSSL=“H”, 64-bit slot L/R sampling clock signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Not used (open)

51 GTOP O

DA11 output when PSSL=“H”, GTOP signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Not used (open)

52 XUGF O

DA10 output when PSSL=“H”, XUGF signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Not used (open)

53 XPLCK O

DA09 output when PSSL=“H”, XPLCK signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”)

54 GFS O

DA08 output when PSSL=“H”, GFS (guard frame sync) signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”)

55 RFCK O

DA07 output when PSSL=“H”, RFCK (read frame clock) signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”)

56 C2PO O

DA06 output when PSSL=“H”, C2PO signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Not used (open)

57 XRAOF O

DA05 output when PSSL=“H”, XRAOF (RAM over flow) signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”) Not used (open)

58 MNT3 O

DA04 output when PSSL=“H”, MNT3 (monitor 3) signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”)

59 MNT2 O

DA03 output when PSSL=“H”, MNT2 (monitor 2) signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”)

60 MNT1 O

DA02 output when PSSL=“H”, MNT1 (monitor 1) signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”)

61 MNT0 O

DA01 output when PSSL=“H”, MNT0 (monitor 0) signal output when PSSL=“L”

(PSSL (pin $£)=fixed at “L”)

62 XTAI I System clock input terminal (16 MHz)

63 XTAO O System clock output terminal (16 MHz) Not used (open)

64 XTSL I System clock selection input terminal (fixed at “L”)

65 DVSS — Ground terminal (digital system)

66 FSTI I 2/3 divider input terminal of pins ^™ (XATI) and ^£ (XTAO)

67 FSTO O 2/3 divider output terminal of pins ^™ (XATI) and ^£ (XTAO)

68 (FSOF)C4M O 4.2336 MHz clock signal output terminal Not used (open)

69 C16M O 16.9344 MHz clock signal output terminal Not used (open)

70 MD2 I Digital out on/off control terminal

71 DOUT O Digital signal (for coaxial out and optical out) output terminal

72 EMPH O Emphasis control signal output terminal Not used (open)

73 WFCK O Write frame clock signal output terminal

74 SCOR O Sub-code sync (S0+S1) detection signal output to the system control (IC801)

Loading...

Loading...