– 19 –

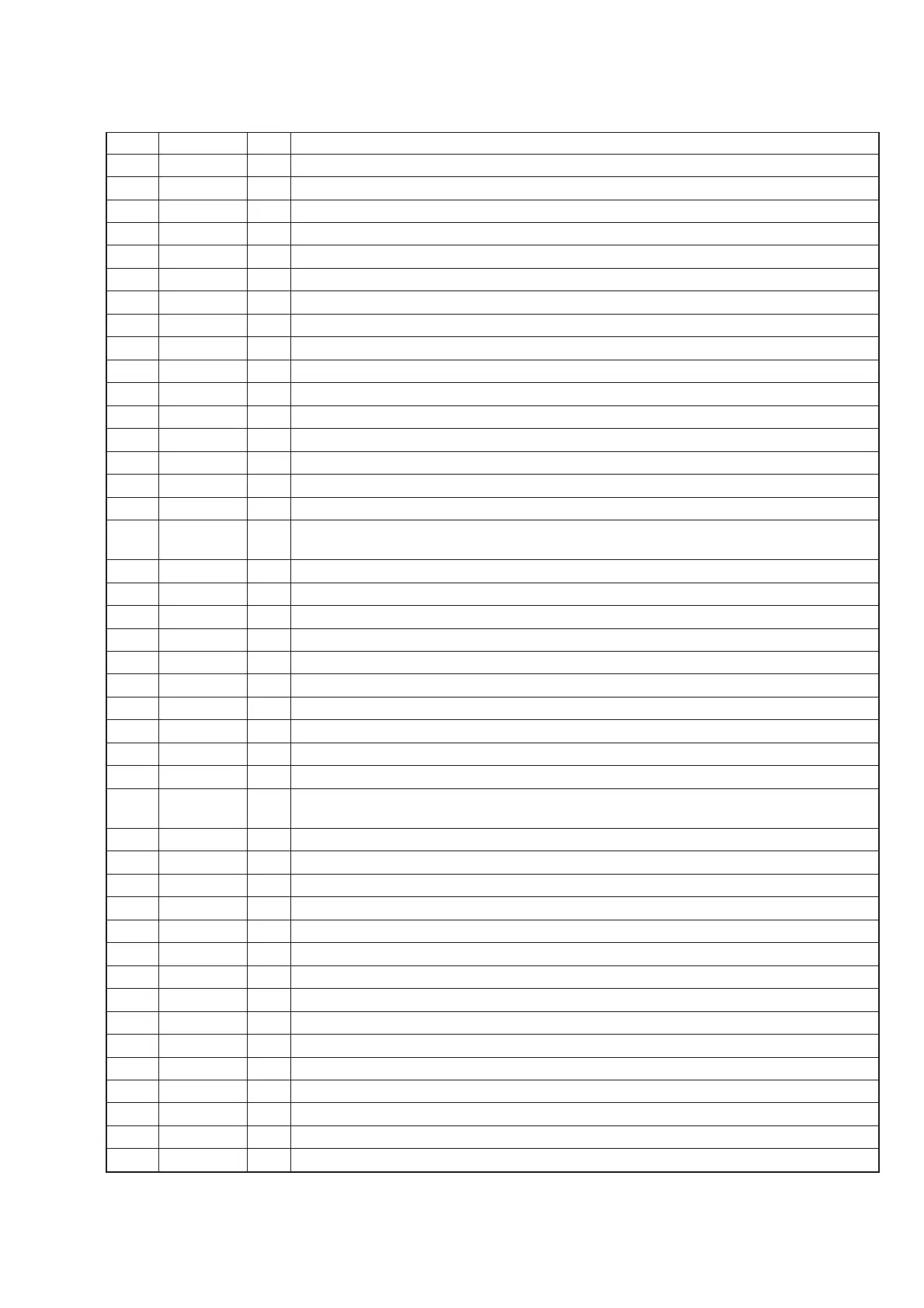

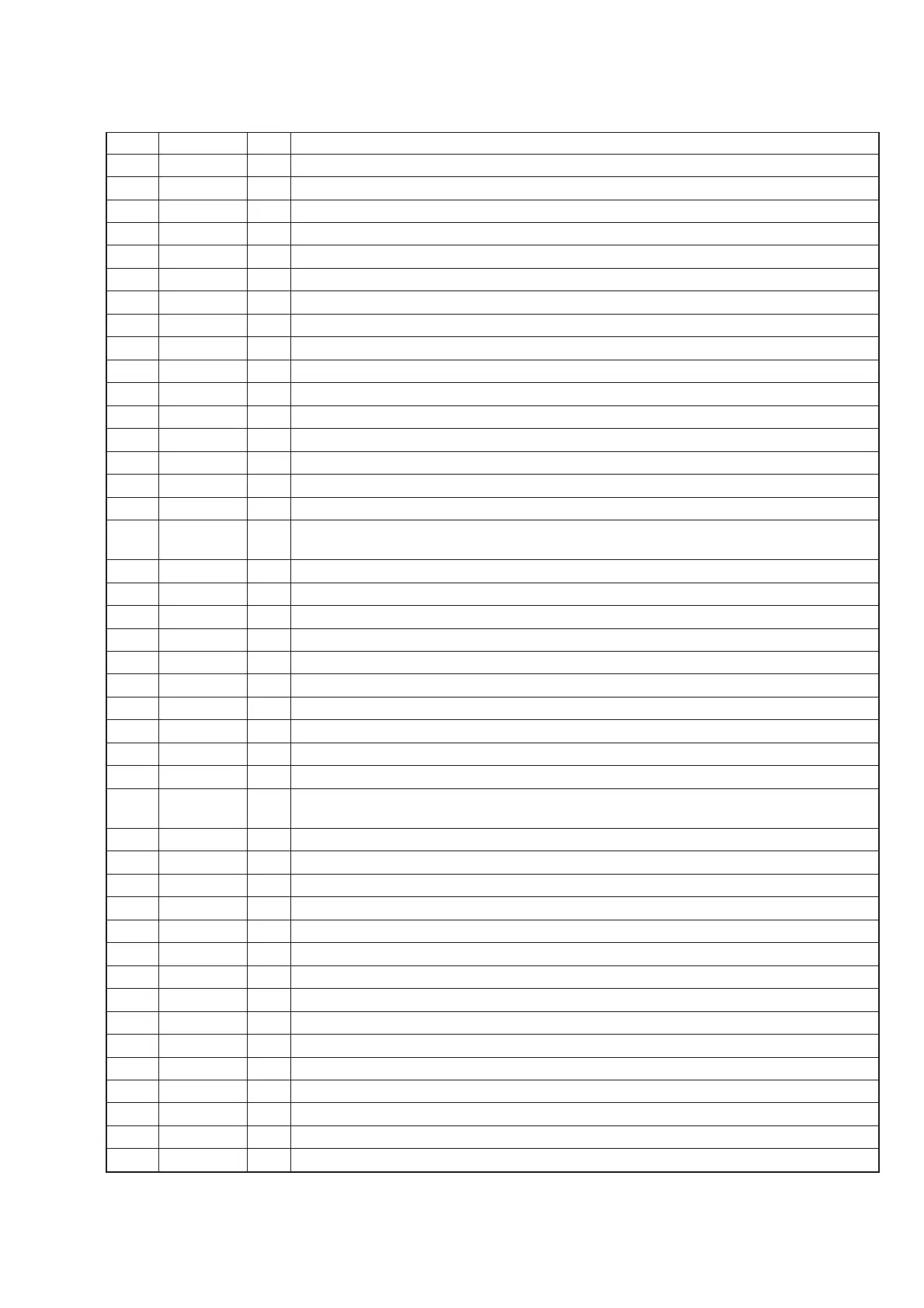

• DISPLAY BOARD IC801 CXP82316-083Q (SYSTEM CONTROL, FLUORESCENT INDICATOR TUBE DRIVER)

Pin No. Pin Name I/O Function

1 TIMER I Not used (fixed at “H”)

2 RM (BUSIN) I Remote control signal input from the remote control receiver (IC802) (AU BUS input)

3 + 5V I Not used (fixed at “H”)

4 OPEN – Not used (open)

5 OPEN – Not used (open)

6 (BUSOUT) O AU BUS output (open)

7 PGML O Program Latch signal output to digital filter CXD8595Q (IC301)

8 CLK O Serial data transfer clock signal output to the CXD2545Q (IC105) and CXD8595Q (IC301)

9 SENSE I Internal status (SENSE) signal input from the CXD2545Q (IC105)

10 DATA O Serial data output to the CXD2545Q (IC105) and CXD8595Q (IC301)

11 SQCK O Sub-code Q data reading clock signal output to the CXD2545Q (IC105)

12 SUBQ I Sub-code Q data signal input from the CXD2545Q (IC105)

13 OPEN – Not used (open)

14 AMUTE O Anolog muting control signal output “H”: mute

15 LDON O Laser diode on/off selection signal output to the RF amplifier in optical pick-up

16 XLT O Serial data latch pulse signal output to the CXD2545Q (IC105)

17 RVLED I

Detection input from the sled limit-out detect switch (S152) The optical pick-up is outer position

when “L”

18 RV+ O Volume up control signal output

19 RV– O Volume down control signal output

20 LDOUT O P LED (D802) drive signal output terminal “H”: LED on

21 LDIN O ” LED (D801) drive signal output terminal “H”: LED on

22, 23 KEY0, 1 I Key data input terminal (A/D input) “L”: on

24 KEY2 I Key data input terminal (A/D input) “L”: on Not used (open)

25 KEY3 I Connected to the @ª pin

26, 27 KEY4, 5 I Key data input terminal (A/D input) “L” on Not used (open)

28 ADJ/AFADJ I Pin for test mode “L”: Test mode

29 IN/OUT SW I Detection input from the loading in/out detect switch (S808)

30 RST I

System reset signal input from the reset signal generator (IC103) “L”: reset For several hundreds

msec. after the power supply rises, “L” is input, then it changes to “H”

31 EXTAL I Main system clock input terminal (4 MHz)

32 XTAL O Main system clock output terminal (4 MHz)

33 VSS – Ground terminal

34 - 41 OPEN – Not used (open)

42 - 62 S21 - S1 O FL segment output

63 - 70 1G - 8G O FL grid output

71 (–30V) VFDP – –30 V pin for FL display tube

72 (+ 5V) VDD – Power supply terminal (+5V)

73 – – Not used (fixed at “H”)

74 SEL1 – Not used (fixed at “L”)

75 – – Not used (fixed at “L”)

76 DACRST O Reset signal output to CXD2562Q (IC302)

77 AMUTE O Analog mute signal output “H” mute on

78 SCOR I Sub-code sync (S0 + S1) detection signal input from the CXD2545Q (IC101)

79, 80 SEL2, 3 – Not used (fixed at “L”)

Loading...

Loading...