ABCDE F

G

HI JKLMN

1

2

3

4

5

6

7

8

9

10

11

- 23 -

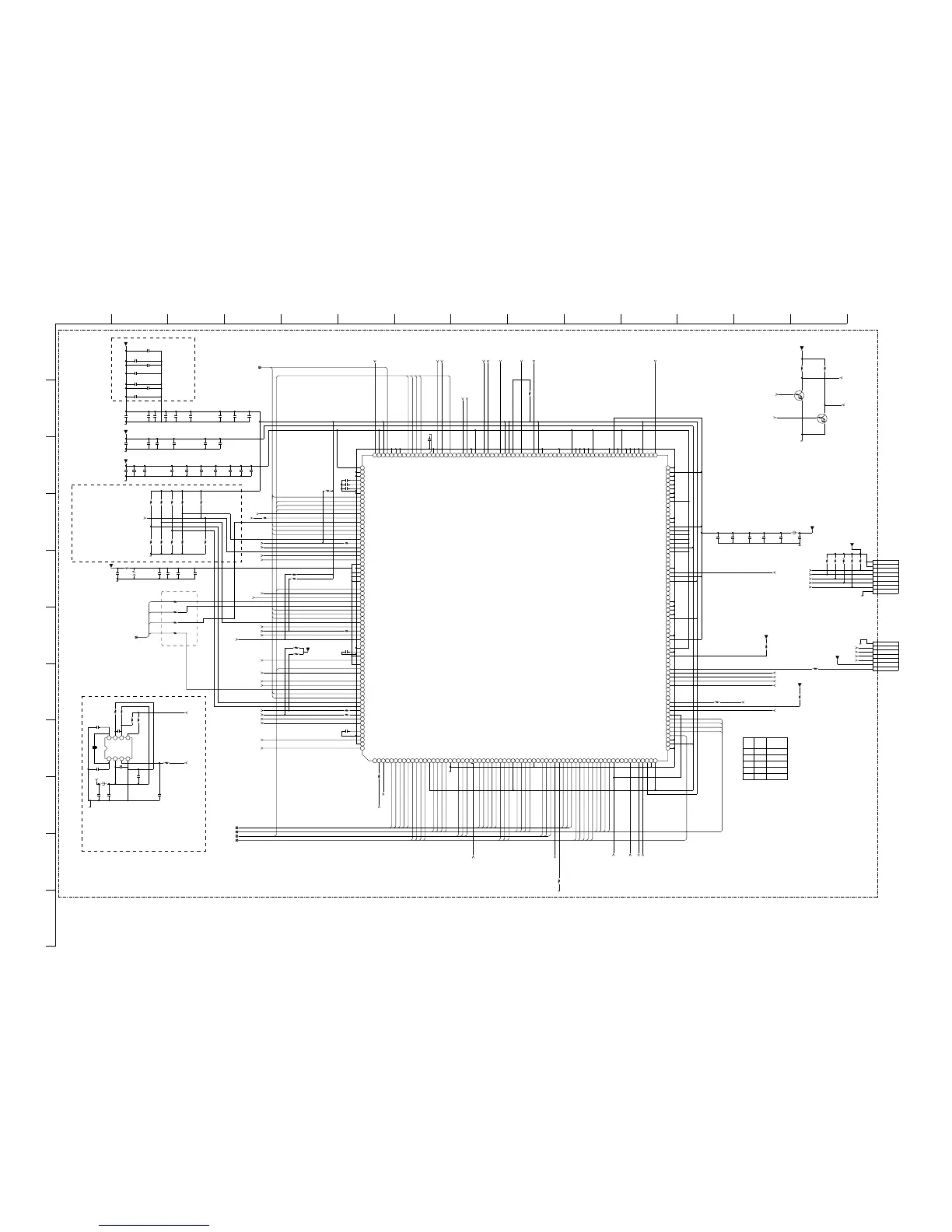

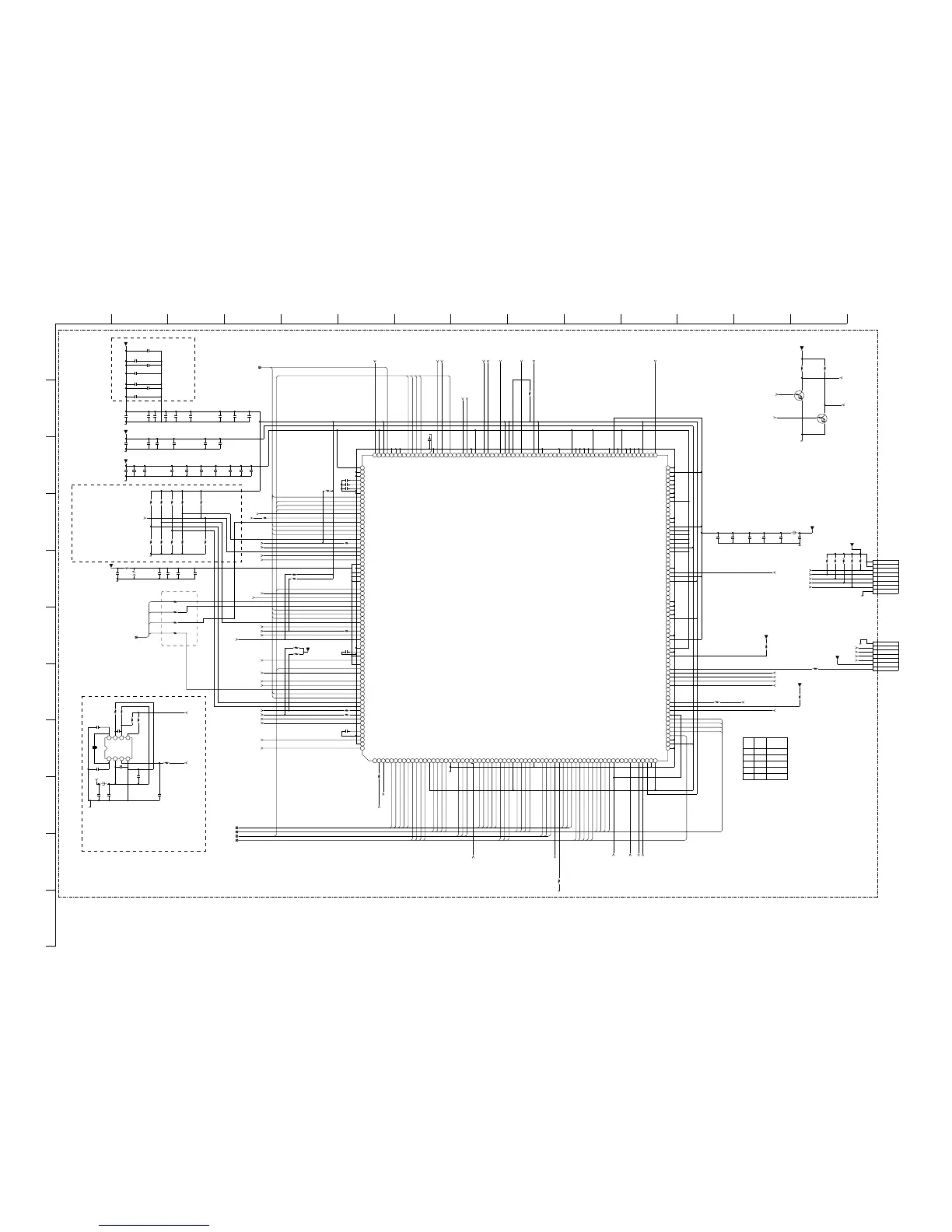

~ B Board Schematic Diagram [ Multimedia Processor & Clock Generator ] Page 1/6 ~

8765

4321

FS6128-04

IC200

X1

VCC

AIN

GND 27M

VCC

GND

X2

PWM_OUT

CLK27M

1000p

C204

13.5MHz

X200

+3V3

10k

R201

SMARTLINK_RX

4.7k

R206

+3V3

JTDO

VAR

+3V3

+1V5

XX

R203

DBA0,DBA1,DCASB,DCLK,DCLKB,DCSB,DQM0,DQM1,DQS0,DQS1,DRASB,DVREF,DWEB

JTMS

RSTOUT

SCL_0

NRBB

STBY_LED_2

GND

NCLE

VACOMP

NALE

TXD_1B

CLK27M

VAY

RDATA[0-15]

AVS_INTB

JTCLK

100R209

SPDIF

DADD[0-12]

RSTSWB

10kR204

FCS1B

FOEB

SDA_0

FWEB

JTDI

DQ[0-15]

VAG

PWM_OUT

JEDINT

RXD_1B

JTRST

VAB

4.7kR205

VAC

IR_IN_0

SMARTLINK_TX

ALRCK,ADO,ABCK,AMCK

STBY_LED_1

JIG_MODE

CHANNEL_UP_SW

CHANNEL_DOWN_SW

STBY_SW

TUNER_RESETB

+3V3

IR_IN_0

RSTSWB

IR_IN_0B

RSTSW

100R208

+2V5

JIG_MODE

1/10W

10k

R240

+3V3

CTS_1B

RTS_1B

SDA_1

SCL_1

+3V3

4.7kR241

4.7k

R242

TXD_1B

RTS_1B

RXD_1B

CTS_1B

10V

4.7

C247

10V

4.7

C248

10V

4.7

C249

10V

4.7

C250

100

R243

100R244

10V

4.7

C259

1/10W

10k

R252

XX

C200

XXC201

0uH

FB200

0uH

FB205

1

2

3

4

5

6

7

8

WHT

8P

CN202

VCC

VCC

JIG_MODE

CTS

RTS

RXD

TXD

GND

STP0_CLK,STP0_DAT[0-7],STP0_EN

1/10W

10k

R253

+3V3

16V

0.1

C207

16V

0.1

C206

16V

0.1

C222

6.3V

1

C246

6.3V

1

C219

6.3V

1

C245

16V

0.1

C220

16V

0.1

C223

+1V5

16V

0.1

C215

16V

0.1

C224

6.3V

1

C227

16V

0.1

C230

16V

0.1

C252

16V

0.1

C254

6.3V

1

C251

6.3V

1

C255

16V

0.1

C260

6.3V

1

C212

10

4.7

C241

1/10W

10k

R256

1/10W

10k

R257

1/10W

10k

R258

10k

R259

XX

R260

XX

R261

XX

R262

XX

R263

0.1

C202

16V

0.1

C203

16V

16V

0.1

C209

16V

0.1

C211

16V

0.1

C213

16V

0.1

C217

0.1

C232

0.1

C233

0.1

C234

0.1

C235

0.1C236

0.1

C238

16V

0.1

C239

16V

0.1

C242

16V

0.1

C210

0.1

C216

16V

47

R264

1/10W

47

R265

1/10W

47

R266

1/10W

47

R267

1/10W

47

R268

33

R200

1/10W

25V

0.01

C218

1/10W

4.7k

R269

1/10W

4.7k

R270

GND

DTC114YUA-T106

Q201

DTC114YUA-T106

Q202

16V

0.1

C244

+3V3

1 2 3 4 5 6 7 8 9 1011121314151617181920212223242526272829303132333435363738394041424344454647484950515253545556575859606162636465

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

161162163164165166167168169170171172173174175176177178179180181182183184185186187188189190191192193194195196197198199200201202203204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

240

231

232

233

234

235

236

237

238

239

241

242

243

244

255

256

245

246

247

248

249

250

251

252

253

254

257

258

259

260

66 67 68

69

72

70

71

75

73

74

78

76

77

81

79

80

84

82

83

87

85

86

88

131

132

133

137

135

136

134

139 138140147159 146158 155 143145160 144157 151 150152154 148156 142 141153 149

264

263

261

262

268

272

271

267

266

265

270

269

UPD61120F1-100-JN1

IC201

CMDVCC0

PPORT34

RXD2B/PPORT53

PPORT49

DADD4

DADD5

DADD7

DADD8

DADD11

DRASB

DCLK

DQM0

DQS1

VDD2

DQ9

DQ11

DQ13

DQ15

GND2

CTS0B/PPORT46

RD ATA 9

RD ATA 2

RDATA10

TXD4B/PPORT52

PPORT48/TXD0B

DADD2

DADD6

DADD10

DADD9

DADD12

DCASB

DQM1

DVREF

VDD2

DQ8

DQ10

DQ12

DQ14

GND2

PPORT45/RTS0B

RD ATA 0

RD ATA 8

RD ATA 1

TXD3B/PPORT54

STP_STRT

DADD3

DADD1

DADD0

DBA1

DBA0

DCSB

DCLKB

DQS0

DQ6

DQ4

DQ2

DQ0

PPORT44

RXD0BP/PPORT47

MMCLK/DTR0B

RADD1

PPORT36

RADD0

PPORT37

RXD3B/PPORT51

PPORT31/OFF1

RADD4

GRDYB

GND

VDD1

SDIN

AVDD1_6

VRCLKIN

RADD6

PPORT28

RADD5

VDD3

GND

AGND1_6

AGND1_266

MCLKIN

RADD24

RADD7

RADD25

FCSB0

VDD3

AVDD1_266

CLK27IN

AGND1_162

RADD15

RADD23

RADD12

VDD1

VDD2

VDD1

VDD1

VDD1

VDD1

AVDD1_162

SYSCLKIN

EVCK

RADD21

RADD16

RADD22

VDD1

GND

GND

GND

GND

GND

AVSYSCLKIN

AVDD1_16

AGND1_16

FEWB

RADD20

PPORT23/SMRST0

VDD3

GND

GND

GND

GND

VDD1

GND

AVDD1_18

AGND1_18

RADD18

RADD14

RADD19

VDD1

GND

FOEB

PPORT27/SMDAT0

RADD11

VDD1

GND

VAC

CTS1B

MMBCLK

GCSB0

RDATA15

RADD10

SMCLK0

VAY

AGND5

CBPF

MMRINGB/PPORT12

RD ATA 6

RDATA13

RD ATA 7

RDATA14

NAND_SEB

GND

GND

GND

STP_DAT7 / PMSDIO

VDD3

VDD1

JTCK

VDD1

GND

GND

CBPC

CBPD

CBPE

AGND4

STP_EN / PMSINS

RDATA11

RD ATA 5

RDATA12

NAND_ALE

ATX

ADO

STP_DAT1

STP_DAT4 / PMSSCLK

STP_DAT6 / PMSPON

TEST

SDA0

JTDI

JTRST

RSTSWB

VAR

AVDD1

AGND2

AVDD3

AVDD4

AVDD5

OFF0/PPORT25

RD ATA 4

NAND_CLE

TXD1B

ALRCK

ABCK

STP_DAT0

STP_DAT3

STP_DAT5/PMSBS

VDD3

GND2

VDD2

GND2

VDD2

GND2

DWEB

DQ7

DQ5

DQ3

DQ1

PPORT41

PPORT42

STPERRB

PPORT22/MMDOUT/DSR0B

RADD3

PPORT32/SMCLK1

RADD2

PPORT33/SMDAT1

IRIN0

PPORT40

FCSB1

PPORT35

GND

GND

GND

VDD1

PPORT17/MMRST

PPORT19/MMMUTEB/RI0B

ACLKIN

RADD8

RADD17

RADD13

GND

VDD3

PPORT13/MMOFFHOOK

PPORT16/MMDIN

MMPWRCNT/DCD0B

PPORT29/SMRST1

RADD9

PPORT30/CMDVCC1

VDD3

VDD3

PPORT10/RTS1B

PPORT11/MMFS

PPORT18/MMHCO

TMODE2

EDINT

SCL0

JTDO

NMI

EIVHS

AGND1

CBPB

AVDD0

VACOMP

AVDD2

RD ATA 3

NAND_R/BB

GCSB1

RXD1B

PWMOUT

AMCK

STP_CLK

STP_DAT2

TMODE0

TMODE1

SDA1

SCL1

EIVVS

CBPA

AGND0

VAG

AGND3

VAB

JTMS

RSTOUT

16V

0.1

C214

1/10W

10k

R271

GND

XX

R272

NMI

1

2

3

4

5

6

7

7P

CN203

GND

E_RX_2

E_RX_3

E_TX_3

E_TX_2

3V3_EMMA

PPORT35

RXD_2B

RXD_2B

TXD_2B

TXD_2B

TXD_3B

TXD_3B

RXD_3B

RXD_3B

+3V3

0

R273

0

R274

XX

R275

SCART_GPO_1

SCART_GPO_2

XX

R276

1/10W

100

R278

10k

R202

50V

1000p

C240

16V

0.1

C262

16V

0.1

C261

10V

4.7

C208

10V

100

C263

0.1

C264

0.1

C265

0.1

C266

0.1

C267

0.1

C268

0.1C269

0.1C270

100uH

L200

1/10W

1k

R277

1/10W

10k

R279

1/10W

10k

R280

10k

R281

10k

R282

DADD[5]

RSTOUT

DCASB

DADD[4]

RDATA[15]

DADD[12]

RD ATA [6 ]

DADD[2]

DQ[15]

RDATA[11]

DADD[10]

RD ATA [0 ]

RDATA[3]

DADD[6]

RDATA[10]

DQ[8]

DADD[8]

DQM1

DVREF

NRBB

DQ[6]

DADD[7]

NCLE

DQS0

STP0_CLK,STP0_DAT[0-7],STP0_EN

RDATA[12]

DCSB

RDATA[0-15]

DBA0

RDATA[5]

DQ[0]

DBA1

DRASB

DADD[11]

RD ATA [2 ]

DQ[2]

DWEB

DADD[9]

DQ[4]

RD ATA [9 ]

STP0_DAT[2]

STBY_LED_2

RDATA[14]

DQ[7]

DQ[5]

DQ[3]

RDATA[4]

DQ[1]

DCLKB

DADD[1]

DADD[3]

DQ[13]

DQM0

DQ[14]

DQ[11]

RD ATA [1 ]

DCLK

RDATA[13]

RD ATA [8 ]

FOEB

RD ATA [7 ]

STP0_DAT[3]

STP0_DAT[0]

STP0_DAT[1]

DQ[9]

DQ[12]

DQS1

DQ[10]

DADD[0]

FWEB

SCL_1

TMODE2

TMODE0

TMODE1

GRDYB

STP0_CLK

ALRCK

ADO

AMCK

ABCK

STP0_DAT[7]

STP0_DAT[5]

STP0_EN

NALE

RSTSWB

IR_IN_0B

IR_IN_0

RSTSW

+3V3

GND

STP0_STRT

USB_INT

STP0_DAT[6]

STP0_DAT[4]

27MHz CLOCK GENERATION

FOR EJTAG:-

FIT R260, R261, R262, R263, R203

NO-FIT R256, R257, R258, R259, R202.

JTAG CONFIGURATION

FOR NORMAL JTAG:-

FIT R256, R257, R258, R259, R202.

NO-FIT R260, R261, R262, R263, R203.

DEBUG CONNECTOR

PLACE CLOSE TO IC201

C260 TO BE PLACED CLOSE

TO PIN 2, IC200

JL219

JL220

JL221

JL215

JL222

MSINS

MSSCLK

MSPON

MSBS

MSDIO

MS INSERTED

SERIAL CLOCK

POWER ON

BUS STATE

DATA IO

JL PIN SIGNAL

MEMORY STICK INTERFACE

PLACE R200 AND R273 -> R275 CLOSE

TO PINS 5 & 6 RESPECTIVELY

R273 -> R275 ARE PROVIDED AS LINK

OPTIONS FOR THE ICS3721

Ground stiching for

3.3V Close to Power

Plane

For Front and Side of PCB

B

B..-VTX-D800

1/6

Loading...

Loading...