PROGRAMMING MANUAL Standard Instruction Set

5/197

1 Standard Instruction Set

1.1 Addressing modes

1.1.1 Short adressing modes

The ST10 family of devices use several powerful addressing modes for access to word, byte

and bit data. This section describes short, long and indirect address modes, constants and

branch target addressing modes.

Short addressing modes use an implicit base offset address to specify the 24-bit physical

address.

Short addressing modes give access to the GPR, SFR or bit-addressable memory space

Note: for byte GPRs, for word GPRs.

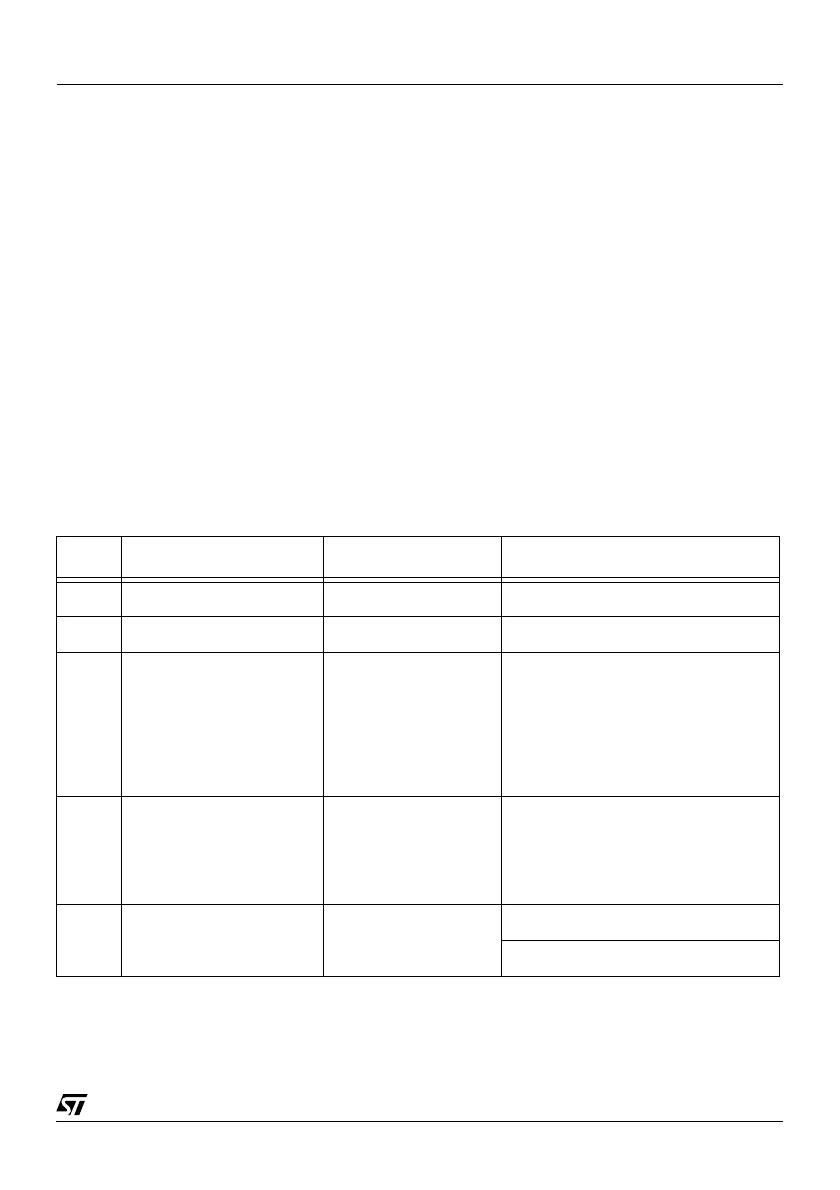

Mnemo Physical Address Short Address Range Scope of Access

Rw (CP) + 2*Rw Rw = 0...15 GPRs (Word) 16 values

Rb (CP) + 1*Rb Rb = 0...15 GPRs (Byte) 16 values

reg 00’FE00h + 2*reg reg = 00h...EFh SFRs (Word, Low byte)

00’F000h + 2*reg reg = 00h...EFh ESFRs (Word, Low byte)

(CP) + 2*(reg^0Fh) reg = F0h...FFh GPRs (Word) 16 values

(CP) + 1*(reg^0Fh) reg = F0h...FFh GPRs (Bytes) 16 values

bitoff 00’FD00h + 2*bitoff bitoff = 00h...7Fh RAM Bit word offset 128 values

00’FF00h + 2*(bitoff^FFh) bitoff = 80h...EFh SFR Bit word offset 128 values

(CP) + 2*(bitoff^0Fh) bitoff = F0h...FFh GPR Bit word offset 16 values

bitaddr Word offset as with bitoff. bitoff = 00h...FFh Any single bit

Immediate bit position. bitpos = 0...15

Table 1 Short addressing mode summary

PhysicalAddress BaseAddress ShortAddress+=

Loading...

Loading...