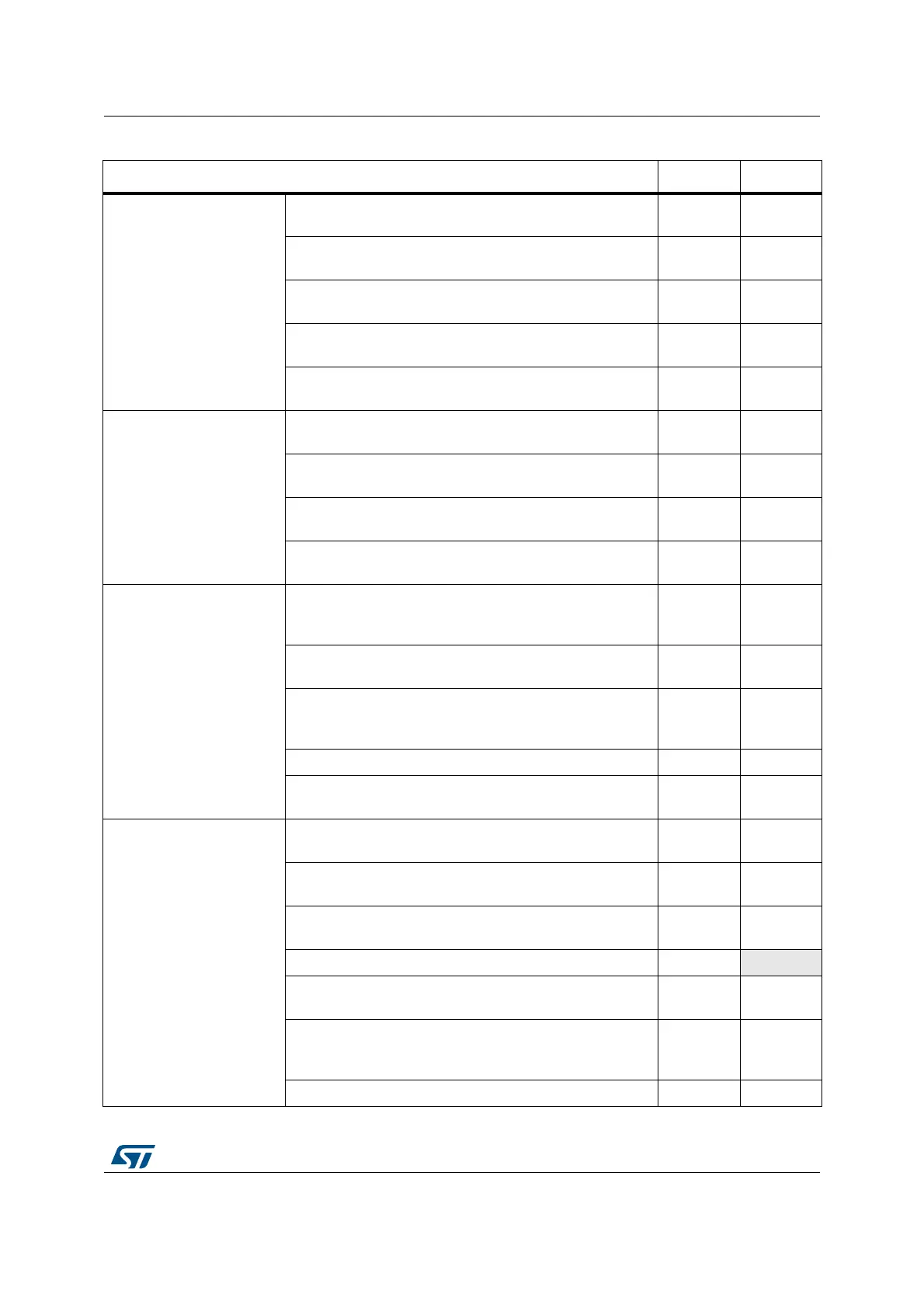

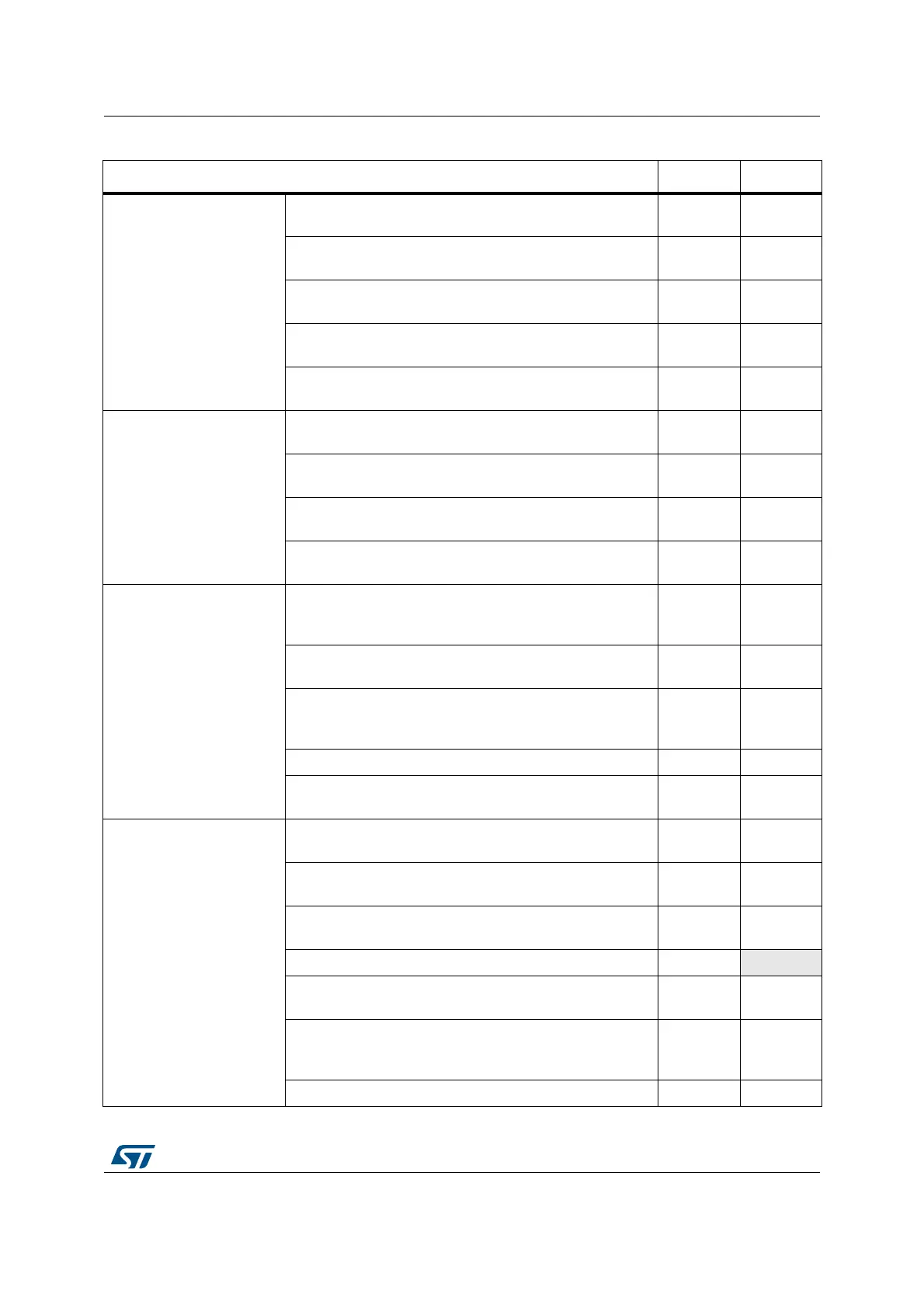

DocID023833 Rev 5 9/36

STM32F42xx and STM32F43xx STM32F42xx and STM32F43xx silicon limitations

35

Section 2.5: USART

peripheral limitations

Section 2.5.1: Idle frame is not detected if receiver clock

speed is deviated

NN

Section 2.5.2: In full duplex mode, the Parity Error (PE) flag

can be cleared by writing to the data register

AA

Section 2.5.3: Parity Error (PE) flag is not set when

receiving in Mute mode using address mark detection

NN

Section 2.5.4: Break frame is transmitted regardless of

nCTS input line status

NN

Section 2.5.5: nRTS signal abnormally driven low after a

protocol violation

AA

Section 2.6: OTG_FS

peripheral limitations

Section 2.6.1: Data in RxFIFO is overwritten when all

channels are disabled simultaneously

AA

Section 2.6.2: OTG host blocks the receive channel when

receiving IN packets and no TxFIFO is configured

AA

Section 2.6.3: Host channel-halted interrupt not generated

when the channel is disabled

AA

Section 2.6.4: Error in software-read OTG_FS_DCFG

register values

AA

Section 2.7: Ethernet

peripheral limitations

Section 2.7.1: Incorrect layer 3 (L3) checksum is inserted

in transmitted IPv6 packets without TCP, UDP or ICMP

payloads

AA

Section 2.7.2: The Ethernet MAC processes invalid

extension headers in the received IPv6 frames

NN

Section 2.7.3: MAC stuck in the Idle state on receiving the

TxFIFO flush command exactly 1 clock cycle after a

transmission completes

AA

Section 2.7.4: Transmit frame data corruption AA

Section 2.7.5: Successive write operations to the same

register might not be fully taken into account

AA

Section 2.8: FMC peripheral

limitation

Section 2.8.1: Dummy read cycles inserted when reading

synchronous memories

NN

Section 2.8.2: FMC synchronous mode and NWAIT signal

disabled

AA

Section 2.8.3: Read access to a non-initialized

FMC_SDRAM bank

PP

Section 2.8.4: Corruption of data read from the FMC A

-

Section 2.8.5: Interruption of CPU read burst access to an

end of SDRAM row

AA

Section 2.8.6: FMC NOR/PSRAM controller: asynchronous

read access on bank 2 to 4 returns wrong data when bank

1 is in synchronous mode (BURSTEN bit is set)

AA

Section 2.8.7: FMC dynamic and static banks switching AA

Table 4. Summary of silicon limitations (continued)

Links to silicon limitations Revision A Revision Y

Loading...

Loading...