50

Super X11SCM-LN8F/-F and X11SCL-LN4F User's Manual

SGPIO Headers

There are two Serial Link General Purpose Input/Output (I-SGPIO1, I-SGPIO2) headers

located on the motherboard. The SGPIO headers are used to communicate with the enclosure

management chip on the back panel.

Chassis Intrusion

A Chassis Intrusion header is located at JL1 on the motherboard. Attach the appropriate cable

from the chassis to inform you of a chassis intrusion when the chassis is opened. Refer to

the table below for pin denitions.

Chassis Intrusion

Pin Denitions

Pin# Denition

1 Intrusion Input

2 GND

IPMI CODE

+

+

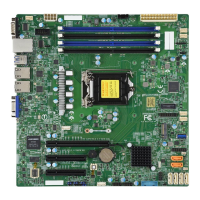

X11SCL-LN4F

REV:1.00

MAC CODE

BAR CODE

DESIGNED IN USA

BIOS LICENSE

LAN4/8

LAN3/7

LAN2/6

LAN1/5

JPL4

JPL8

JPL3

JPL7

JPL2

JPL6

JPL1

JPL5

FAN4

COM1

IPMI_LAN

USB0/1

USB4/5

(3.0)

VGA

JLD2

JLD1

JPW2

JPW1

FAN2

FAN1

LED_PWR_SB

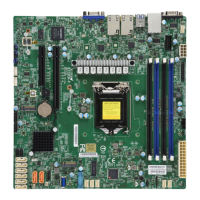

X11SCM-LN8F/-F

Intel

C246 / C242

2280

22110

2280

BMC_HB_LED

LED4

JUIDB1

JWD1

JPME2

JPG1

JBAT1

SP1

USB2/3

JTPM1

I-SGPIO1

I-SGPIO2

JBT1

I-SATA3

I-SATA2

I-SATA1

I-SATA0

I-SATA5

I-SATA4

JL1

FANB

FANA

JSD2JSD1

JSTBY1

USB8

(3.0)

JLED1

JF1

FAN3

PWR_LED

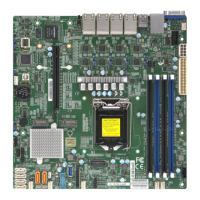

ASpeed

AST2500

M.2-P_1

M.2-H_2

JD1

USB6/7 (3.0)

CPU

DIMMA1

DIMMA2

DIMMB1

DIMMB2

22110

NMI

JF1

LED

PWR

X

LED

HDD

NIC

LED

UID

2

NIC

1

RST

PWR

ON

FAIL

PS

CPU SLOT6 PCI-E 3.0 X16

Intel

i210

Intel

i210

1. Chassis Intrusion Header

2. I-SGPIO1 Header

3. I-SGPIO2 Header

1

2

3

SGPIO Header

Pin Denitions

Pin# Denition Pin# Denition

1 NC 2 NC

3 GND 4 DATA Out

5 Load 6 GND

7 Clock 8 NC

NC = No Connection

I-SGPIO 1/2

I-SGPIO1 I-SATA 3.0 Ports 0-3

I-SGPIO2 I-SATA 3.0 Ports 4-5

Loading...

Loading...