Page 47

11.1.6 Six blinks alarms

1) STBY I HIGH

Cause: It occurs if the rest state current signals (measured on the phases U

and W) are not in the window 2.5±0.3Vdc after switching on the key

and 2.5±0.15Vdc when in the steady state. These voltage are

measured between D46 and D45 anodes and gnd.

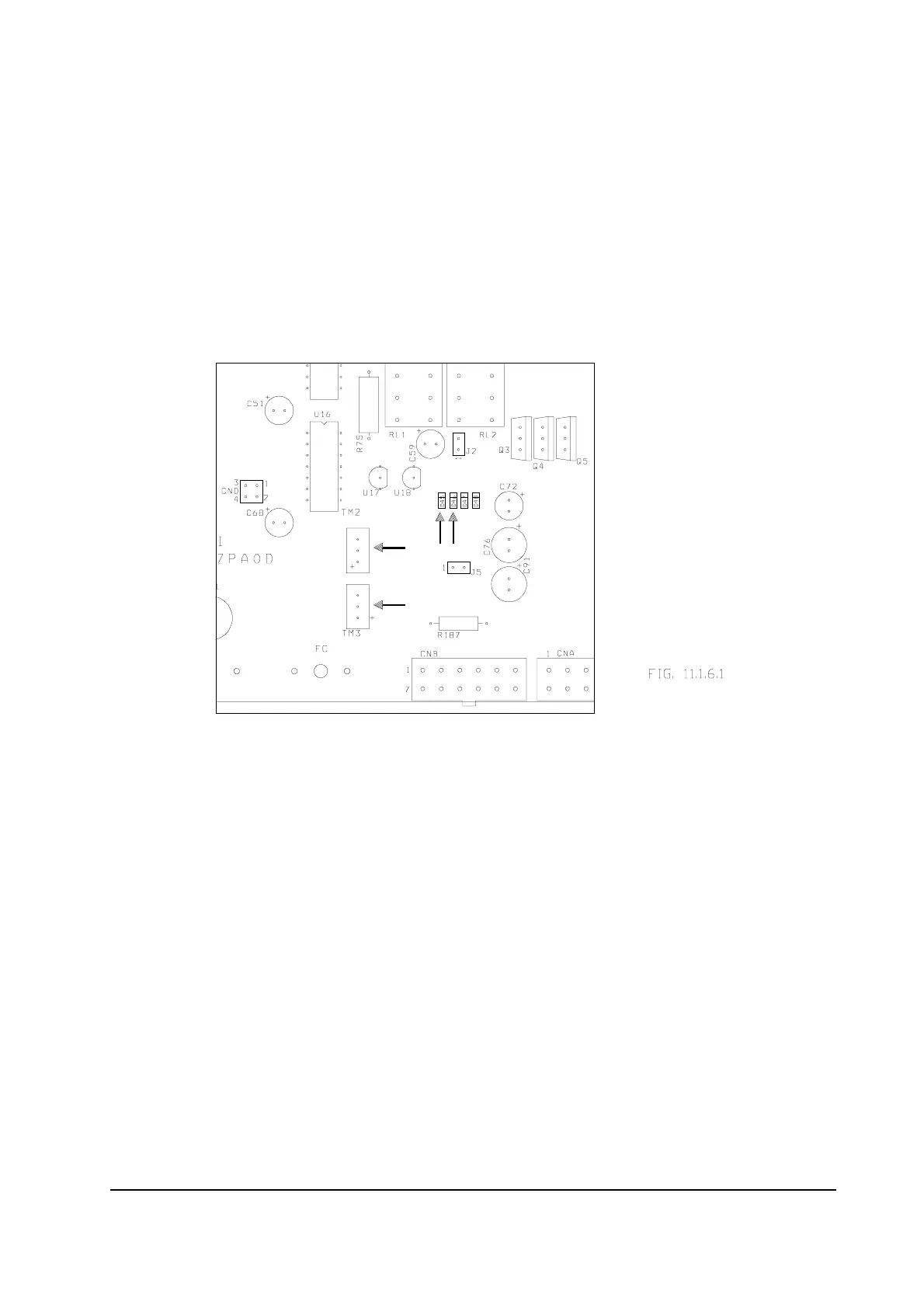

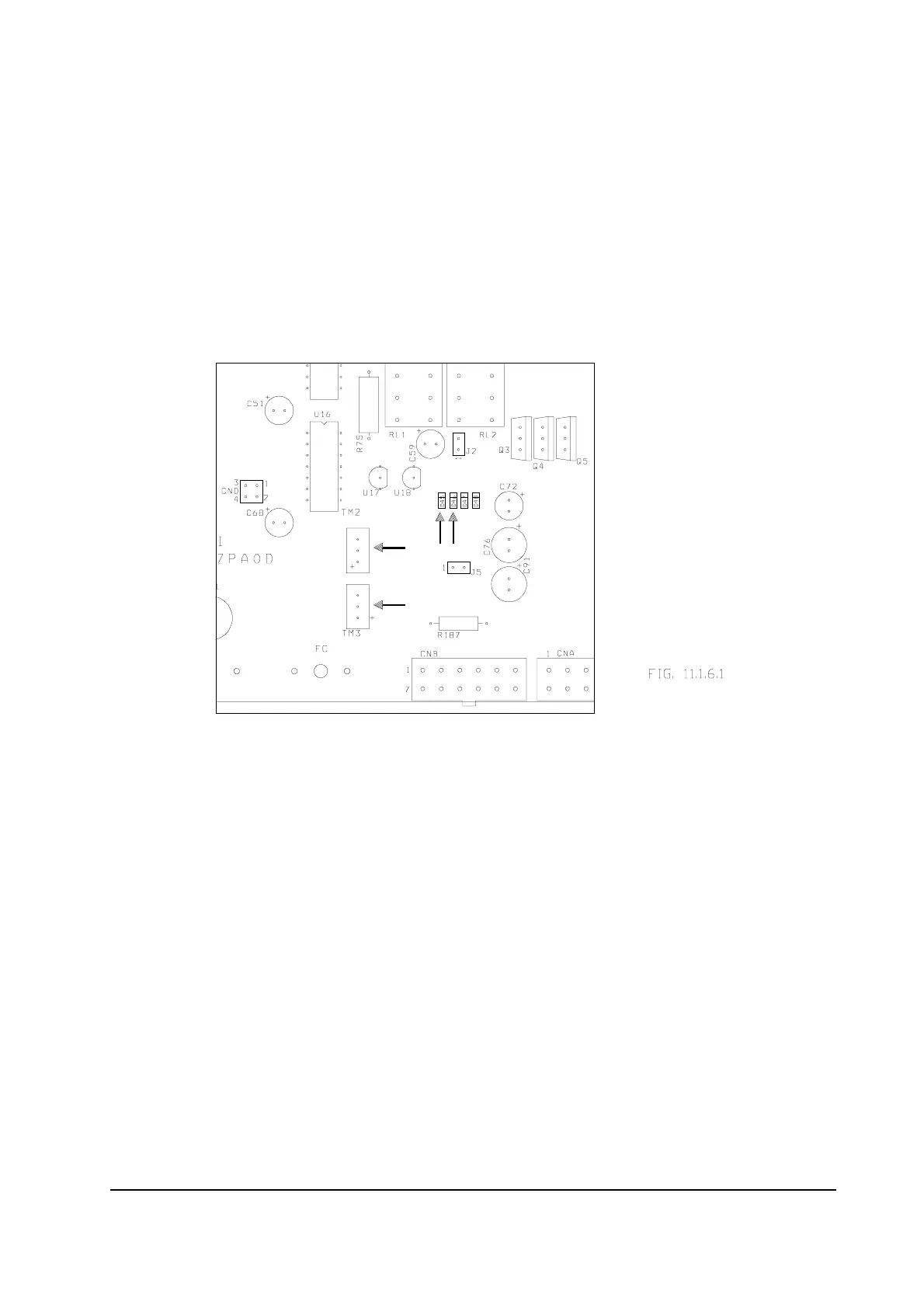

Remedy: The 2.5Vdc rest state values should be TM3 (for D46) and TM2 (for

D45) factory adjusted. If the problem is not due to TM3 or TM2

settings, to try a logic substitution.

2) VMN NOT OK

Cause: It occurs when in the initial rest state at least one of the phases of

the motor voltage is high: that means the voltage between D47 and

D48 anodes and gnd are not in the window 2.5±0.3Vdc (see Fig.

11.1.6.2).

Remedy: If the alarm occurs permanently, it is necessary to substitute the

logic.

3) LOGIC FAILURE #3

Cause: It occurs when in the rest state the Vv-Vu phase motor voltage is

high: that means the voltage between D47 anode and gnd is not in

the window (Vv-Vu)0±0.25Vdc (see Fig. 11.1.6.2).

Remedy: If the alarm occurs permanently, it is necessary to substitute the

logic.

Loading...

Loading...