Page 18

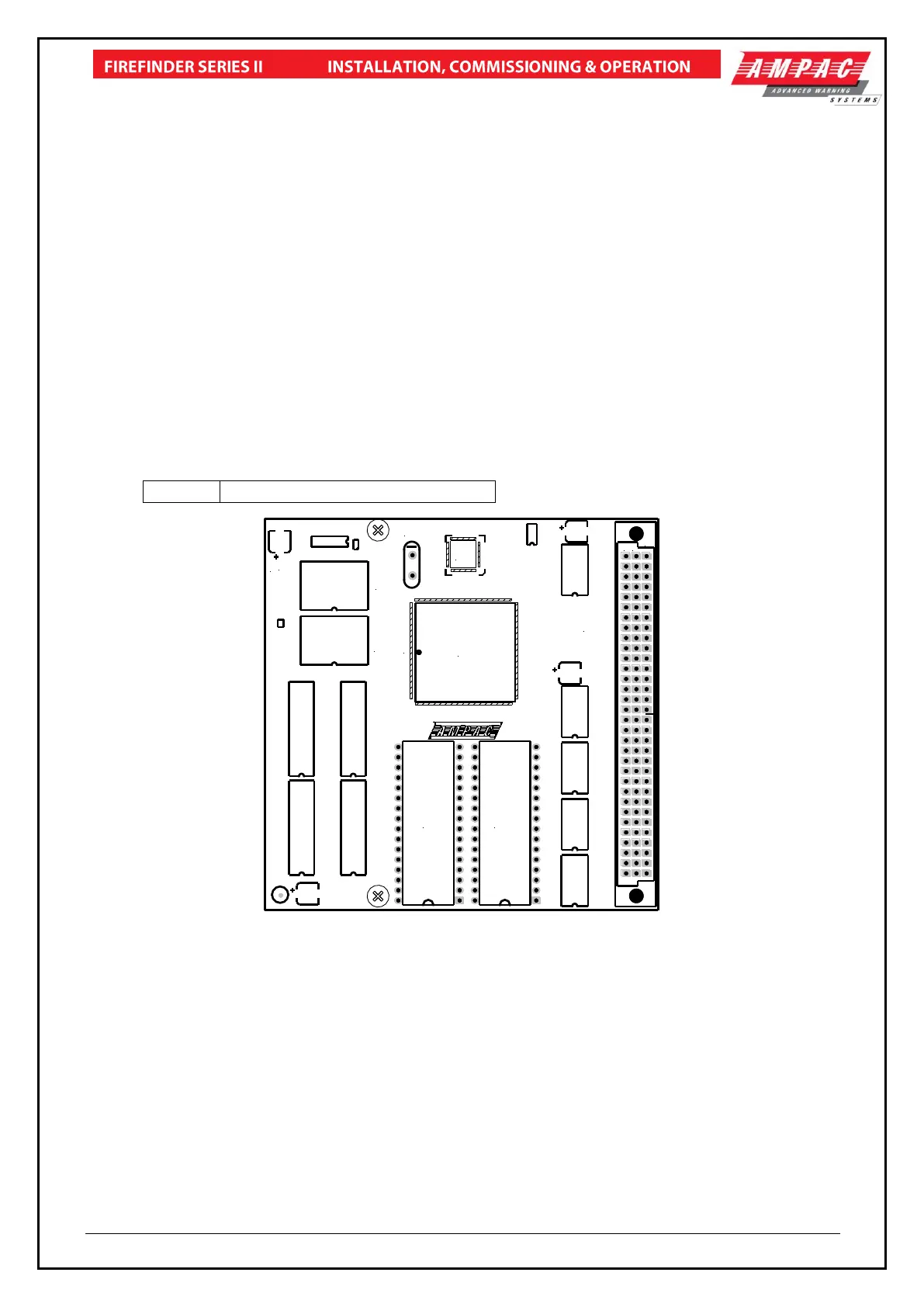

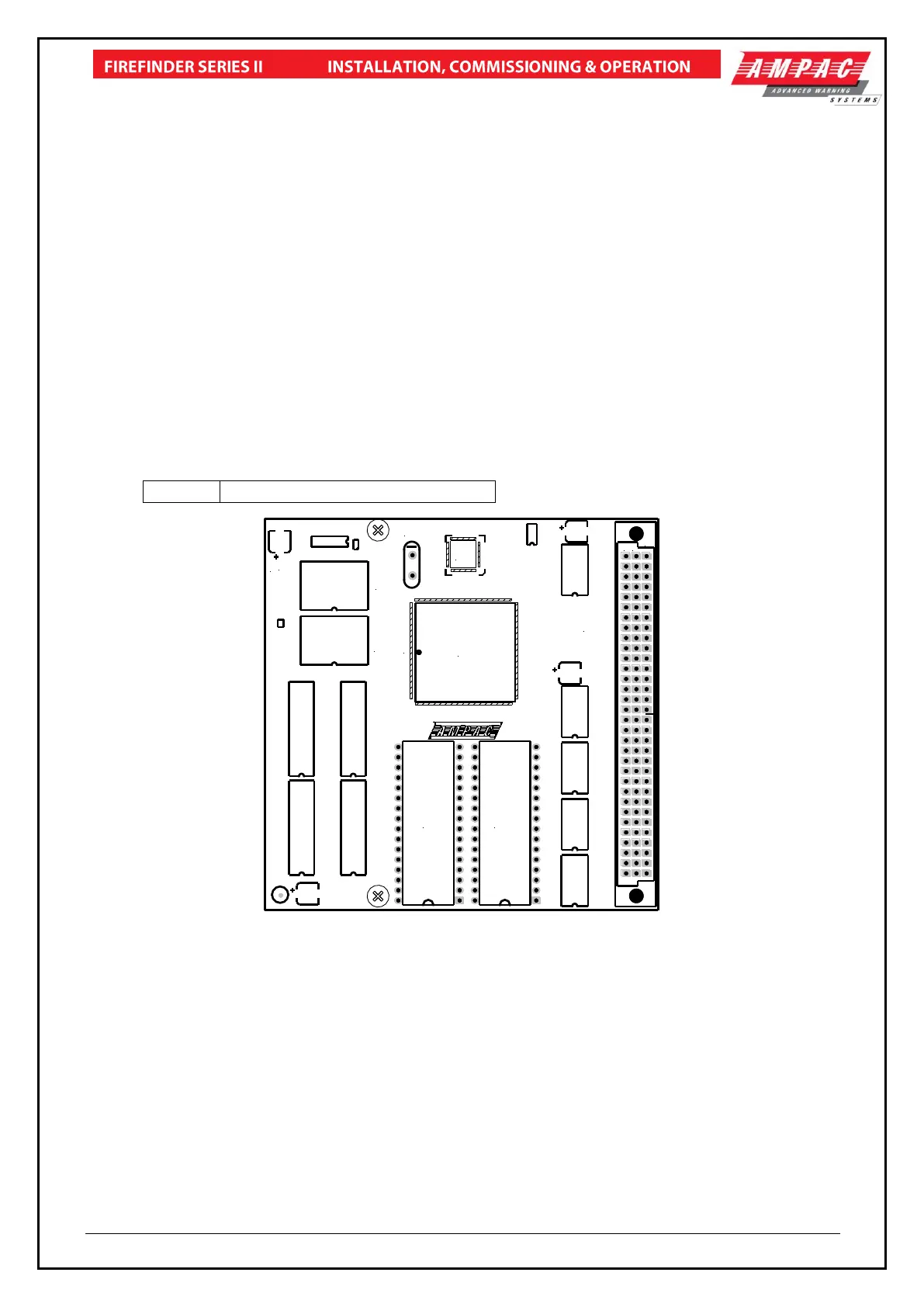

4.13 Main CPU (BRD85CPU)

The Main CPU holds the main central processing unit for the FACP.

BRD85CPU is a 4-layer surface mount board

The processor (U1) is a Motorola MC68302, running at 20MHz.

The external data bus is 16 bits wide.

The board has 256 Kbytes (128K x 16) of EPROM (U2, U3).

2Mbytes (1M x 16) of FLASH (U6, U9).

2Mbytes (2M x 16) of static RAM (U4, U5, U16, U17).

U8 is a programmable logic device which implements control signal timing and decoding.

External address, data and control lines are buffered by U10, U11, U13, U14 and U15.

U7 is a watchdog control and will reset the processor if there as an error in software

execution.

Two sockets (U2 and U3) are provided for M27C1001 EPROMS. U2 provides the even

bytes. (D0 toD7) and U3 the odd bytes (D8 to D15

Connections

To Main Board BRD85MBA CN11

U1

U8

U6

1

XL1

CN2

a b

c

U9

U2

U3

BRD85CPU3-

06/01/2004

Figure 19: The Main CPU Board PCB Layout

Loading...

Loading...