Do you have a question about the ARTERY AT32F403A Series and is the answer not in the manual?

Interface functions for hardware clock configuration in BSP are encapsulated and can be called.

Figure 2 shows the clock configuration process.

Demonstrates setting up a 240 MHz system clock using HEXT/2 and PLL.

Specifies the software requirements, primarily Windows 7 and above.

Instructions for installing the clock configuration tool by running the executable.

Introduces the basic operations of the graphical clock configuration tool.

Describes the options available in the tool's menu bar for project management and settings.

Steps to initiate a new clock configuration project within the tool.

Explains the main blocks and elements of the graphical interface for clock setup.

Process of generating source files after configuring clock paths and frequencies.

Guidance on modifying the HEXT clock frequency from the default 8 MHz for actual applications.

Key notes and best practices for using the New Clock Configuration tool effectively.

Configuration process and code for switching system clock between 64 MHz and 96 MHz.

Describes expected outcomes when switching system clocks and using the USER button.

Configuration and code for enabling clock fail detector and NMI interrupt.

Details behavior during clock failure and rescue operations using HICK.

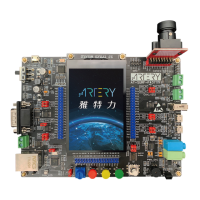

| Series | AT32F403A |

|---|---|

| Core | ARM Cortex-M4 |

| GPIO Pins | Up to 80 |

| Operating Temperature | -40°C to +85°C |

| ADC | 12-bit, up to 16 channels |

| DAC | 12-bit |

| Communication Interfaces | USART, SPI, I2C, USB, CAN |

| Package | LQFP48, LQFP64 |