Do you have a question about the ARTERY AT32F413 Series and is the answer not in the manual?

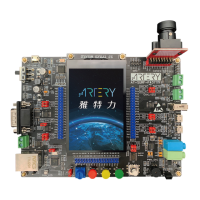

Provides an overview of the AT32F413 series microcontrollers, covering core features, peripherals, and architecture.

Details the features of the ARM Cortex-M4F processor, including its DSP instructions and FPU support.

Illustrates the memory address mapping for Flash, SRAM, and peripheral registers within the microcontroller.

Describes the organization and architecture of the on-chip Flash memory, including bank configurations.

Introduces the power supply, temperature range, and power-saving modes of the AT32F413 series microcontrollers.

Highlights key features of the power control unit, including power domains, saving modes, and voltage detection.

Details the various clock sources available, including HEXT, HICK, PLL, LEXT, and LICK oscillators.

Explains the system clock selection and switching mechanism among HICK, HEXT, and PLL clocks.

Describes the CRM_CTRL register bits for controlling clock sources, bypass modes, and calibration.

Explains how to select the clock output source for the CLKOUT pin, including various peripheral clocks.

Details the CFDFC bit for clearing the clock failure detection flag and enabling interrupt requests.

Describes the ACC reset bit, which enables resetting the ACC peripheral.

Details the CAN2 reset bit, allowing software to reset the CAN2 peripheral.

Describes the SDIO1EN bit for enabling the SDIO1 clock in normal, Sleep, or Deepsleep modes.

Controls the ACC clock enable, allowing it to be enabled or disabled.

Enables or disables the clock for the CAN2 peripheral.

Controls the RTC clock enable, allowing it to be enabled or disabled.

Indicates if a low-power reset has occurred, cleared by writing to RSTFC bit.

Allows setting the frequency division of the CLKOUT signal, providing flexibility in clock output.

Enables automatic system clock switching, ensuring smooth transitions between clock sources.

Provides an introduction to the Flash memory, detailing its structure, capacity, and page organization.

Describes the procedure for unlocking and locking the Flash memory block for programming operations.

Details the step-by-step process for programming the Flash memory, including checks and data writing.

Explains how to unlock and lock the user system data area for programming operations.

Covers Flash memory access protection, detailing allowed operations and conditions for enabling/disabling.

Describes the security library, its protection mechanisms, advantages, and configuration steps.

Details the FLASH_PSR register, which is reserved and kept at its default value.

Introduces General-purpose I/Os (GPIOs), their grouping, main features, and support for multiplexed functions.

Defines the GPIOx configuration register low bits for setting GPIO function and mode.

Introduces multiplexed function I/Os (IOMUX) and their support for various peripherals.

Controls the event output functionality, allowing redirection of Cortex-M EVENTOUT signal to I/O pins.

Configures SPI1 IO multiplexing, allowing selection of different pins for SPI communication.

Introduces the EXINT controller, its interrupt lines, and edge/software trigger capabilities.

Explains the DMA controller's role in enhancing system performance by managing peripheral access requests.

Configures DMA channel settings including priority, transfer direction, address increment, and circular mode.

Introduces the Cyclic Redundancy Check (CRC) peripheral, following the CRC32 standard.

Introduces the I2C bus interface for microcontroller communication, supporting master and slave modes.

Explains how the I2C clock is achieved by setting CLKFREQ bits in the I2C_CTRL2 register.

Describes the I2C_CTRL1 register, covering peripheral reset, SMBus alert, PEC transfer, master acknowledge, and GENSTOP/GENSTART bits.

Introduces the USART peripheral, its capabilities for synchronous and asynchronous communication, and supported protocols.

Explains the USART mode selector for operating in different modes like LIN, Smartcard, Infrared, and Synchronous.

Describes the SPI interface, its configurations (host/slave, full/half-duplex), DMA transfer, and CRC function.

Introduces the I2S interface, its configuration as master/slave for reception/transmission, and supported audio protocols.

Provides a comparison of timer functionalities, including counter bit, mode, prescaler, and interrupt capabilities.

Introduces the general-purpose timer (TMR2 to TMR5), its counting modes, capture/compare registers, and PWM output.

Lists the registers for TMR1 and TMR8, including control, status, and channel mode registers.

Details the main features of general-purpose timers TMR9 and TMR12, including clock sources and channels.

Explains the count clock sources for general-purpose timers, including internal, external, and internal trigger inputs.

Describes the TMR9_CTRL1 register bits for clock division, period buffer, counting mode, and overflow event source.

Configures the slave timer mode, input selection, and synchronization with the master timer.

Provides the interrupt status flags for TMR9 channels, including recapture and trigger interrupt flags.

Introduces the advanced-control timers TMR1 and TMR8, highlighting their 16-bit counter and capture/compare features.

Introduces the window watchdog timer, its purpose for preventing system resets, and its clock source.

Lists the WWDT registers, including control, configuration, and status registers.

Introduces the WDT, its low-speed clock source (LICK), and suitability for low-timing accuracy applications.

Introduces the RTC as a calendar clock function with an internal 32-bit incremental counter.

Details the RTC functional overview, including register configuration, synchronization logic, and reset behavior.

Describes the RTC_CTRLH register bits for enabling overflow, alarm, and second interrupts.

Introduces battery powered registers located in the battery powered domain, powered by VDD/VBAT.

Introduces the ADC peripheral, its function of converting analog signals to digital, sampling rate, and channel count.

Details channel management for ADCs, including analog signal channel inputs and channel conversion groups.

Explains the power-on and calibration process for the ADC, including clock configuration and calibration steps.

Describes ADC trigger mechanisms, including ordinary and preempted channel triggers, software triggers, and external events.

Introduces the Controller Area Network (CAN) protocol, its features, and version support.

Provides a general description of the CAN controller, highlighting filtering mechanisms, FIFOs, and identifier support.

Introduces the USBFS, its implementation of USB2.0 full-speed protocols, bus speed, and endpoint capabilities.

Details the USBFS endpoint configuration, including number, transfer types, buffer allocation, and status.

Introduces HICK auto clock calibration (HICK ACC), its purpose for USB clock accuracy, and calibration algorithm.

Introduces the SD/SDIO MMC card host interface, its connection to AHB bus, and compatibility with various card specifications.

Describes the card functional description, including command types, addressible commands, and operational modes.

Introduces the debug features of Cortex-M4F, including halt, single step, trace, and debug interfaces like SWD and JTAG.

| Series | AT32F413 |

|---|---|

| Core | ARM Cortex-M4 |

| Flash Memory | Up to 256 KB |

| SRAM | Up to 32 KB |

| GPIO Pins | 51 |

| ADC | 12-bit, up to 16 channels |

| DAC | 12-bit, 2 channels |

| Timers | Advanced, general-purpose, basic timers |

| Communication Interfaces | I2C, SPI, USART, CAN |

| Operating Temperature | -40°C to 85°C |

| Package Options | LQFP48, LQFP64 |

| DMA Channels | 7 |