3 - 2

2. CONNECTOR LOCATION AND PIN LAYOUT

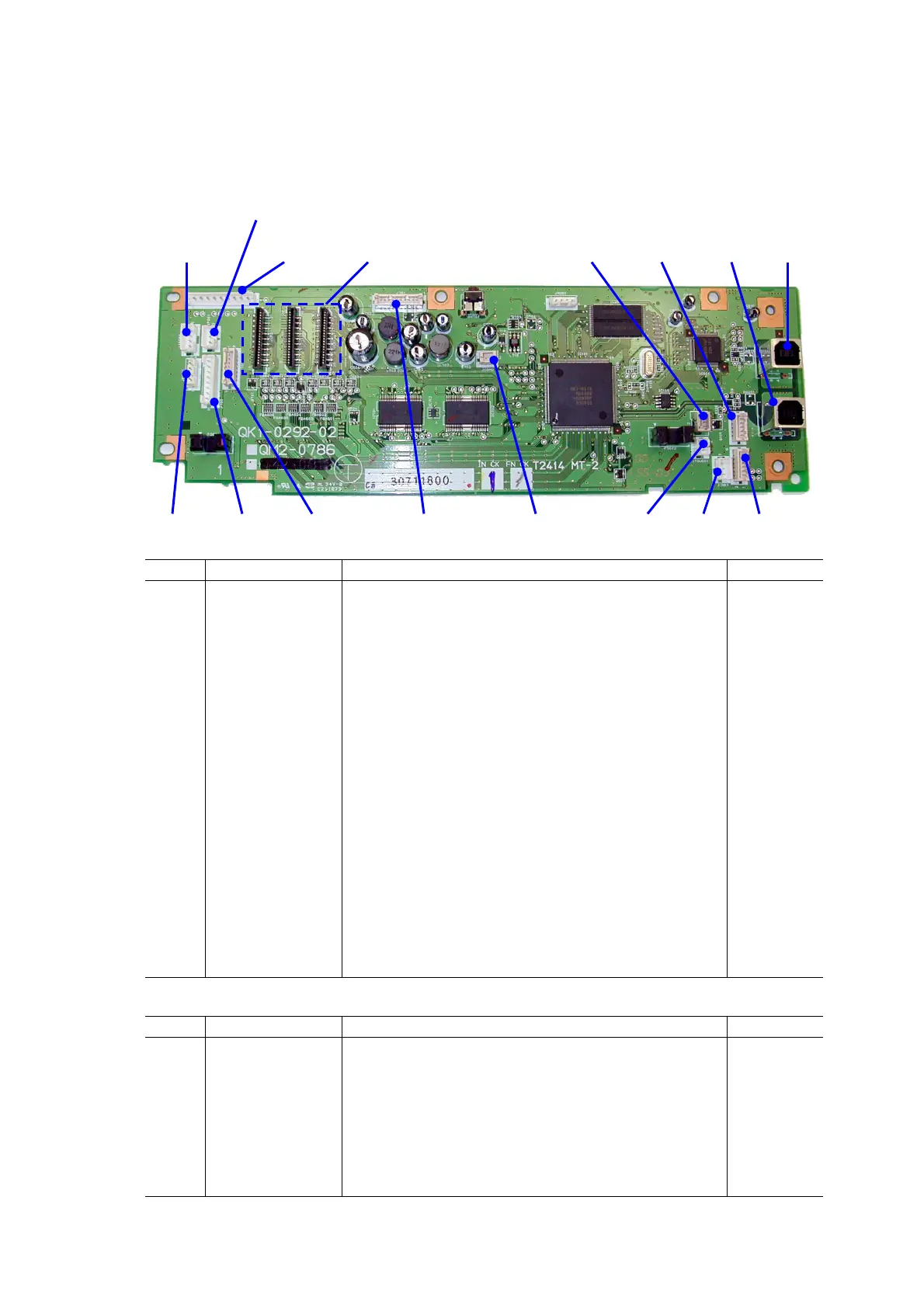

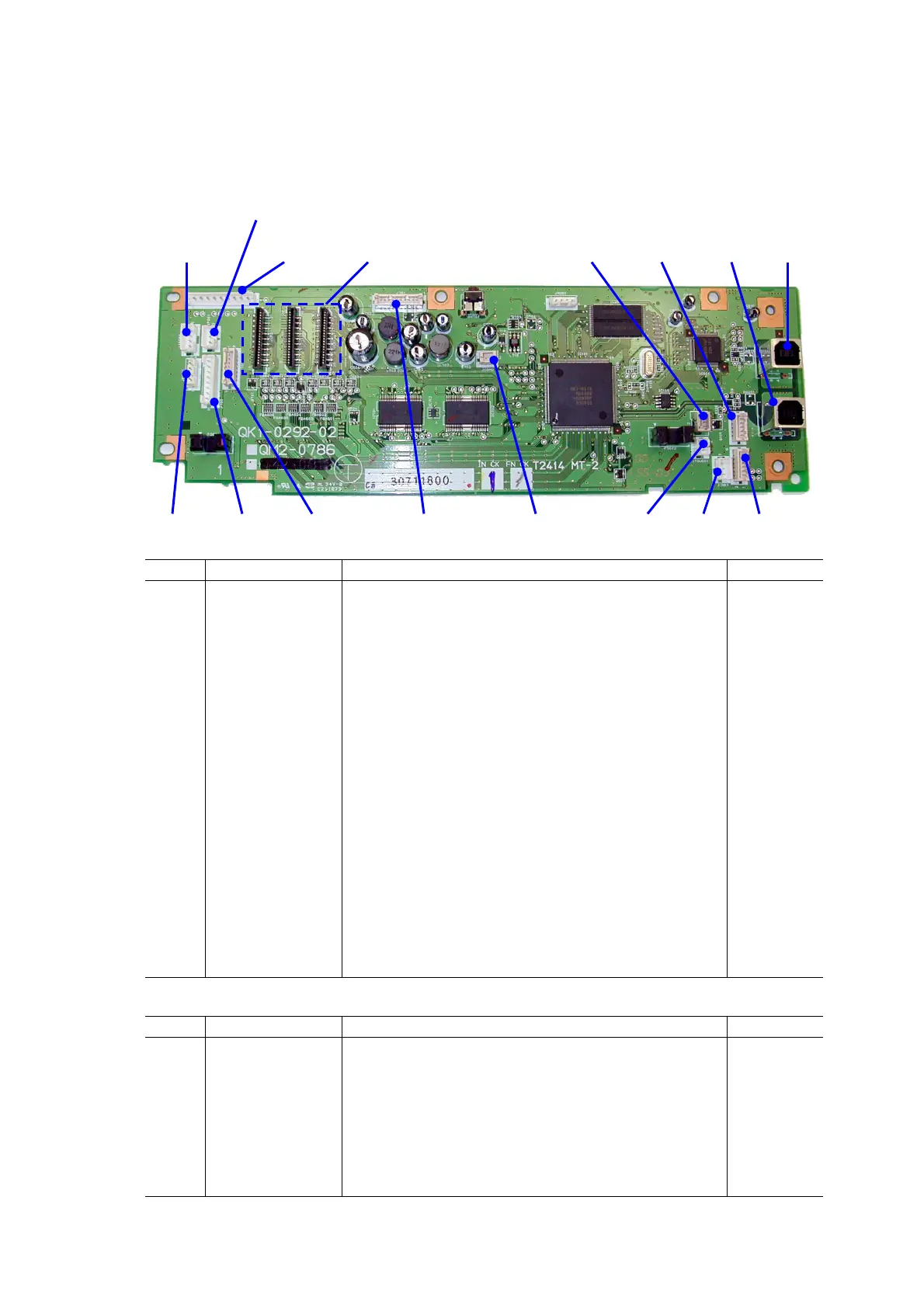

2.1 Logic Board Ass’y

JCR1 (Print head 1/3 [Carriage Unit])

No. Signal name Function Input/Output

1 CDR_PWM CDR sensor PWM signal Out

2 CRENCA CR encoder phase A In

3 EVDD Sensor power supply 5V Out

4 CRENCB CR encoder phase B In

5 GND GND -

6 CDR_WID_SNS CDR sensor signal Out

7 GND GND -

8 HCLK Head data transmission clock signal Out

9 GND GND -

10 DATAK Data BK Out

11 DHE Head enable dummy nozzle Out

12 HEEP_SK Head EEPROM serial clock signal Out

13 BG Transmission clock clutch signal Out

14 DATALC Data LC Out

15 HEEP_CS Head EEPROM chip select signal Out

16 TSOCLC Status output C, LC Out

17 HECX Head enable C Out

18 DATAC Data C Out

19 HELCX Head enable LC Out

20 HEKX Head enable BK Out

JCR2 (Print head 2/3 [Carriage Unit])

No. Signal name Function Input/Output

1 to 6 GND GND -

7 DATALM Data LM Out

8 TSOKY Status output BK, Y Out

9 DATAY Data Y Out

10 HDSEN Head presence detection signal In

11 HEEP_WD Head EEPROM data signal Out

12 to 14 HVDD Head logic drive power 3.3V Out

15 to 20 VH Head drive power 16V Out

JUSB3JUSB2 JCR3 / JCR2 / JCR1 JPOW

J757

JPGS1

J755 JPGM2

JASFS2

JLFENC2 JTGUDS1 JINK1

JBSP1

J762

J761 JCRM2

Loading...

Loading...