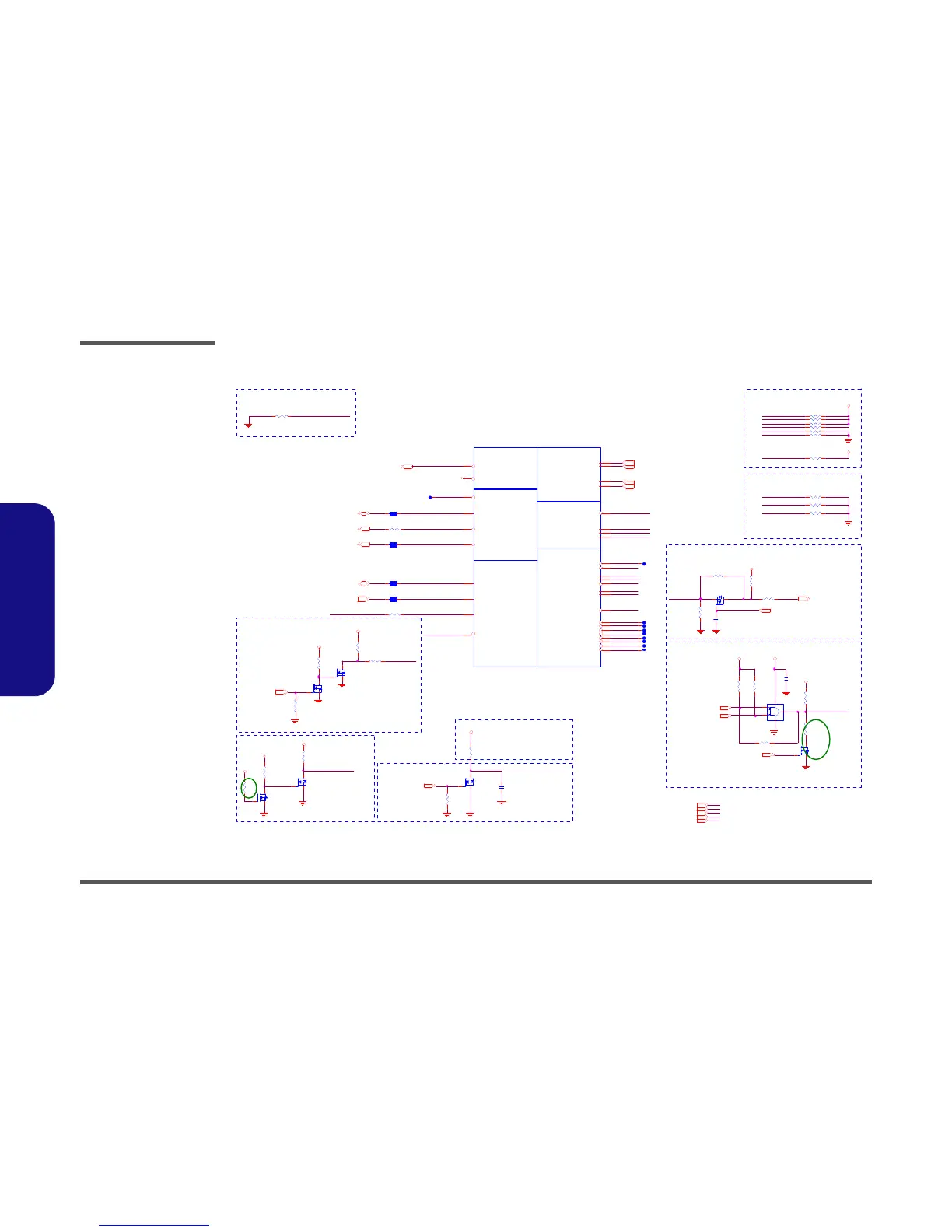

H_PROCHOT#

H_C PUPW R GD _ R

1.5V6,9,10,25,29,33,35, 37,38

H_ PECI23,34

H_PM_SYNC20

C AD No te : Ca pac it or

n eed t o be p lac ed

c los e to b uf fer

o utp ut p in

3 . 3V _E N _ D

1.5VS_C PU_PW R GD

TRACE WIDTH 10MIL, LENGTH <500MILS

H_CPU PW R GD_ R

Processo r Pull d owns

R572

*1 0K _0 4

BU F_CPU _RST#

12 /1

Ad d

PU/PD for JTAG sign al s

1.05VS_VTT2 , 5, 2 3 , 2 4, 25 , 3 5 , 37 , 3 9

CL K_ BC LK 1 9

1. 5 V S _ C P U6,35

3.3V2,8,11,16, 18,19,20,22,23,24,25,27,28,29,30,35,37,38,39

CL K_ D P 1 9

CL K_ D P# 1 9

CL K_ BC LK# 1 9

DR AMR ST_ CNTR L 8 ,19

3.3VS9,10,11,12,18,19,20,21, 22,23,24,25,27,28,30, 31,32,33,34,35,39

H_CPU PW R GD23

H_PR OC HOT#_ EC34

XD P _ D B R _R

H_PROCHOT#39

SM_RC OM P_2

SM_RC OM P_1

SM_RC OM P_0

XD P _ TR S T #

XD P _ TC L K

VD DPW R GO OD _R

H_PR OC HO T# _R

XD P _ TM S

CPU_DRAMRST#

XD P _ P R E Q #

XD P _ TD I _ R

XD P _ TD O _ R

R401 *10mil_short_04

R148

*3 9 _0 4

R222 *0_04

R441

75_04

C135

47p_50V_NPO _04

R440

100K_04

R220

1K_04

R88

62_04

R403 1K_04

R400 *10mil_short_04

Q1 3

*MTN 7002ZHS3

G

DS

R82 *10 mil_sh o rt_04

S

D

G

Q31B

L2N7002DW 1T1G

5

34

R39910K_04

R439

43 _ 1 % _ 0 4

R147

*2 0 0 _0 4

S

D

G

Q31A

L2N 7002DW 1T1G

2

61

R156

*10K_04

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U29B

P Z 98 8 2 7- 3 6 4 B - 0 1F

SM _R CO MP[1 ]

A5

SM _R CO MP[2 ]

A4

SM _DRA MRS T#

R8

SM _R CO MP[0 ]

AK 1

BCLK#

A27

BCLK

A28

DPL L _R EF_ SSCL K#

A15

D PLL_R EF_SSCLK

A16

CATERR#

AL3 3

PEC I

AN33

PR OC HO T#

AL3 2

THER MTR IP#

AN32

SM _D RA MPW R OK

V8

R ESET#

AR33

PRD Y#

AP 29

PR EQ#

AP 27

TCK

AR 26

TMS

AR 27

TRS T#

AP 30

TDI

AR 28

TD O

AP 26

DBR#

AL35

BPM# [0]

AT28

BPM# [1]

AR 29

BPM# [2]

AR 30

BPM# [3]

AT30

BPM# [4]

AP 32

BPM# [5]

AR 31

BPM# [6]

AT31

BPM# [7]

AR 32

PM _S YN C

AM34

SKTO CC #

AN34

PR OC _S ELEC T#

C26

UNCOREPWRGOOD

AP33

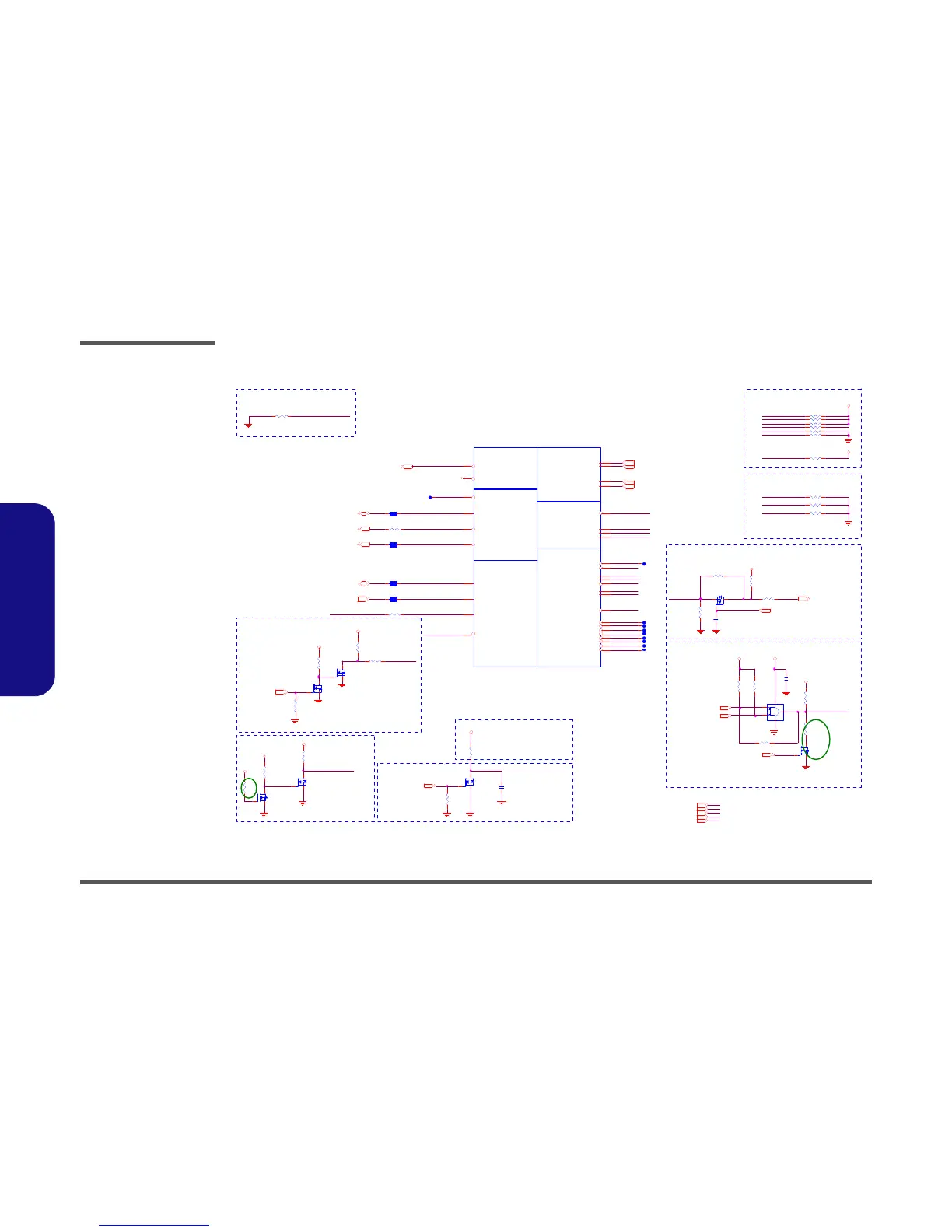

Q10

MTN7002ZH S3

G

DS

TRACE WIDTH 10MIL, LENGTH <500MILS

Processor Pull up

Q16

*MTN7002Z HS3

G

DS

R153

*100K_04

R91 56_1% _04

R420 51_04

R443 200_1%_04

R402 *10mil_short_04

R414 51_04

R436

10K_04

R 144 130_1% _04

C652

0.047u_10V_X7R _04

R145

20 0 _ 1% _ 0 4

R418 51_04

R446 140_1%_04

R217 1K_04

Q2 0

MTN7002Z HS3

G

DS

R416 51_04

R 150 0_04

C248

* 0.1u_16V_Y5V_04

R442 25.5_1%_04

R415 *51_04

H_PM _S YN C_R

R218

4.99K _1% _04

R157

*10K_04

U10

*74AHC1G09

1

2

5

4

3

R410 51_04

R94

100K_04

If PR OC HO T# i s not u se d,

th en it m us t be te rm in at ed

wi th a 56 -O + -5 % p ul l- up

re sis to r to 1 .0 5VS _V TT .

DDR3 Comp ensatio n Si gnals

B UF_CPU _RST#

SM_RC OM P_1

SM_RC OM P_0

SM_RC OM P_2

3.3VS

1. 05 V S _ V T T

DDR 3_D RAM RST # 9,10

H _SN B_IVB#23

H_THRMTRIP#23

XD P _ B P M 0 _ R

XD P _ B P M 1 _ R

XD P _ B P M 2 _ R

XD P _ B P M 4 _ R

XD P _ B P M 3 _ R

XD P _ B P M 5 _ R

XD P _ B P M 6 _ R

XD P _ B P M 7 _ R

XD P _ P R D Y #

PM SYS_PWR GD _BUF

Q17

*BSS138_NL

G

DS

PLT_RST#12,22,28

PM_ D RAM _PW RGD20

SU SB35,37,38

1. 5V S _C P U _ P W R G D38

H_THR MTR IP#_R

S3 circui t:- DRAM PWR G OOD logic

Sandy Bridge Processor 2/7 ( CLK,MISC,JTAG )

12/1

???

Buffered reset t o CPU

3. 3 V S

1.5VS_CPU

3. 3 V

3.3V 3.3V

1.5V S_C PU

1. 5 V

1.05VS _VTT

3.3VS

1.05VS _VTT

H_PEC I_ R

CPU _ DRA MR ST#

S3 circui t:- DRAM_RST # to memor y

should be high du ring S3

XDP_D BR_R

H_C ATERR #

XD P_TR ST#

H _SNB_ IVB#

XD P _ TD O _ R

XD P _ TC L K

XD P _ TD I _ R

XD P _ TM S

XD P_PREQ #

PMS YS_PW R GD _BU F

Loading...

Loading...