13

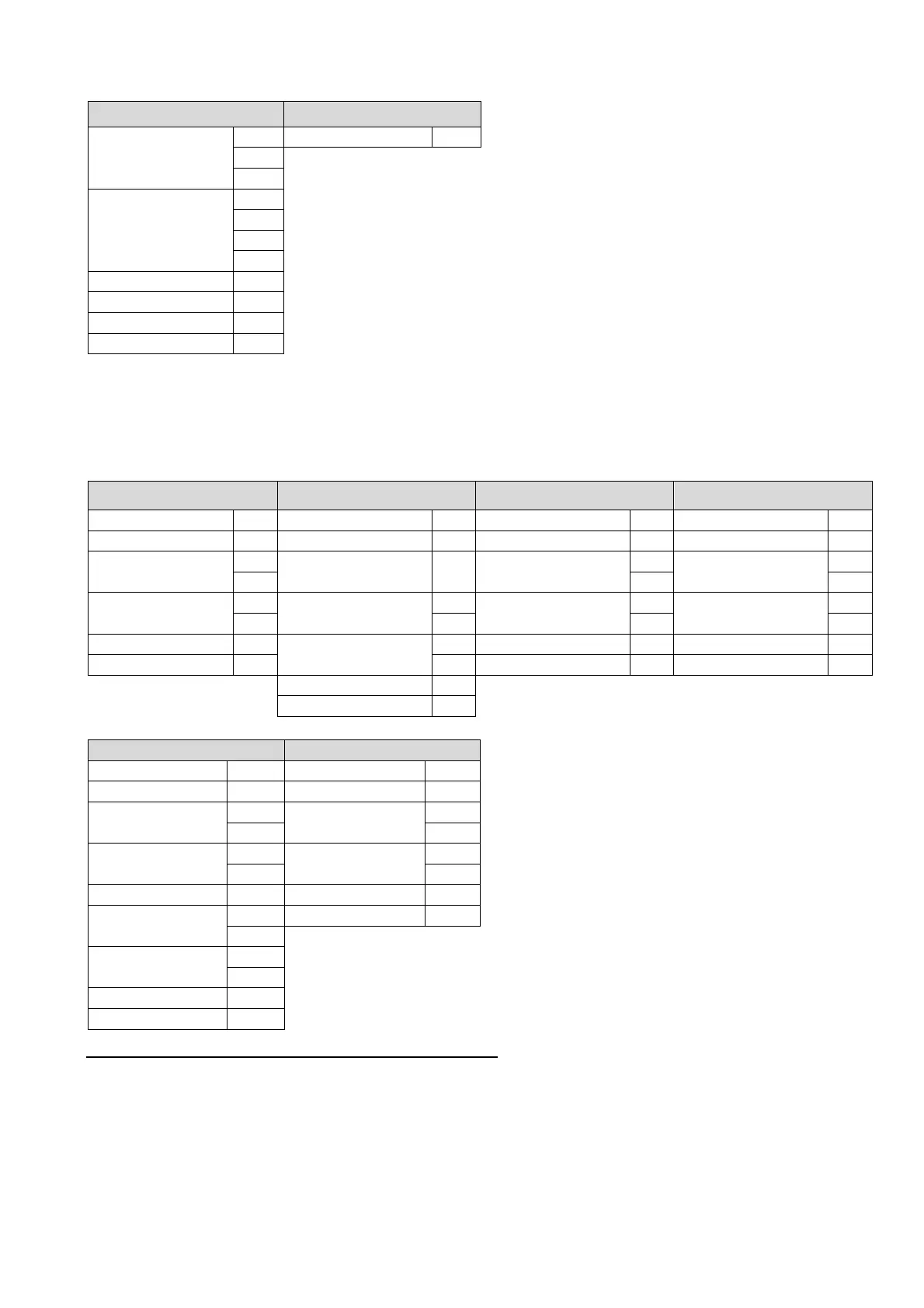

Multi Write Command Multi Write Response Command

‘0’ End word 0 LF

‘6’

‘0’

Write data content 2

‘0’

‘0’

‘1’

‘5’

LRC1 check ‘F’

LRC0 check ‘4’

End word 1 CR

End word 0 LF

LRC Check:

Sum up the contents from “machine address” to “data content”, e.g. H01 + H03 + H10 + H00 + H00 + H02 = H16. Obtain 2’scomplement

HEA.

RTU Mode:

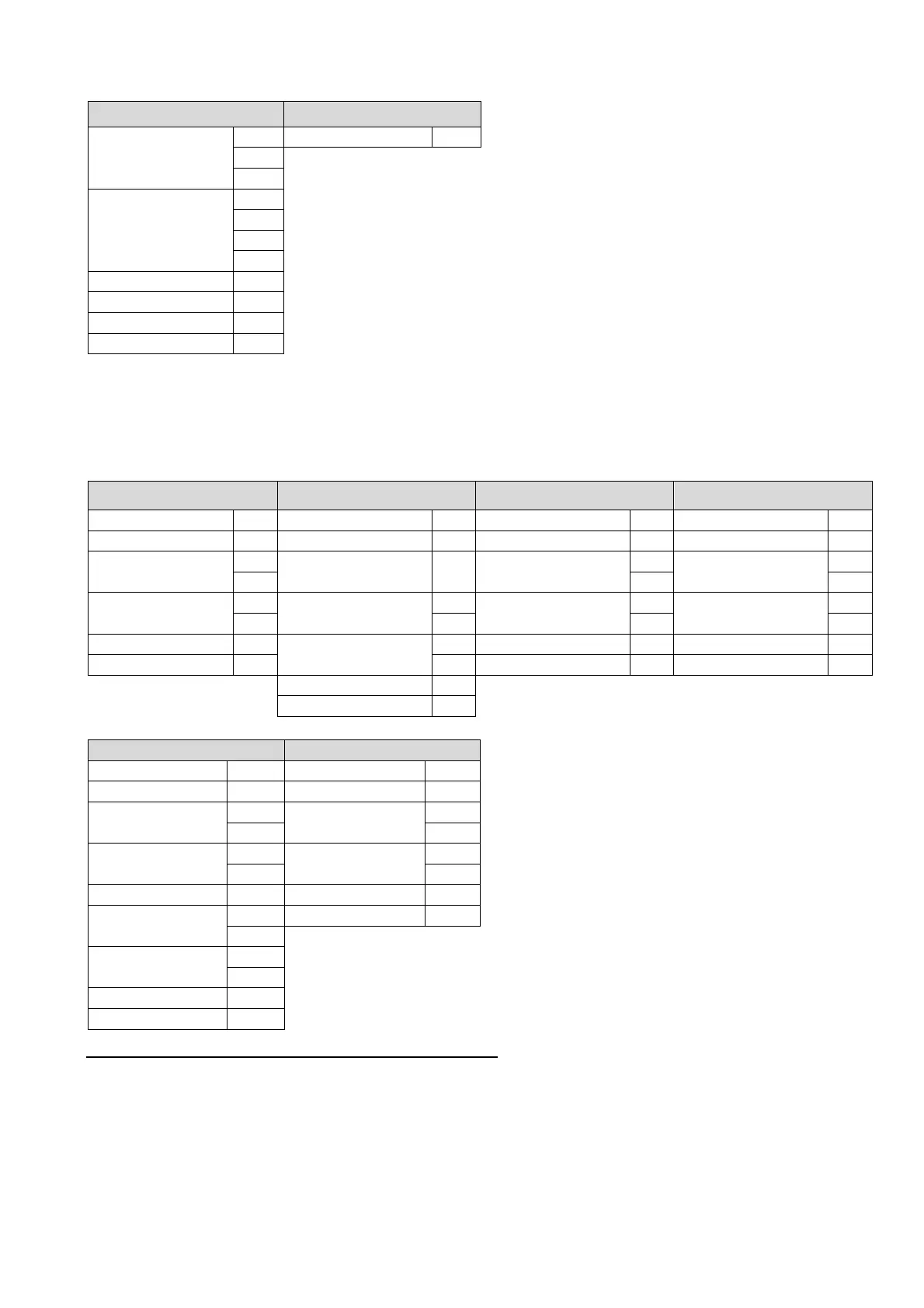

Single read and write:

Read Command Read Response Message Write Command Write Response Message

Machine address H01 Machine address H01 Machine address H01 Machine address H01

Command H03 Command H03 Command H06 Command H06

Read start address of

data

H10

Length of response data

(byte)

H04 Write data address

H10

Write data address

H10

H00 H01 H01

Read length of data

(bit/word)

H00

Data content 1

H01

Write data content

H03

Write data content

H03

H02 HF4 H20 H20

CRC low byte HC0

Data content 2

H03 CRC low byte HDD CRC low byte HDD

CRC high byte HCB H20 CRC high byte HE2 CRC high byte HE2

CRC low byte HBB

CRC high byte H15

Multi write: maximum 32 words

Multi Write Command Multi Write Response Command

Machine address H01 Machine address H01

Command H10 Command H10

Write data address

H10

Write data address

H10

H70 H70

Number of words

H00

Number of words

H00

H02 H02

Number of bytes H04 CRC low byte H44

Write data content 1

H00 CRC high byte HD3

H60

Write data content 2

H00

H15

CRC low byte HF8

CRC high byte H9A

CRC (Cyclical Redundancy Check) is obtained by the following steps:

unsigned int reg_crc = 0xffff;

i = 0;

while (length--)

{ reg_crc ^= RTUData[i];

i ++;

for (j = 0; j < 8; j++)

{ if (reg_crc & 0x01) reg_crc = (reg_crc >> 1) ^ 0xA001;

else reg_crc = reg_crc >> 1;

}

}

return(reg_crc);

Loading...

Loading...