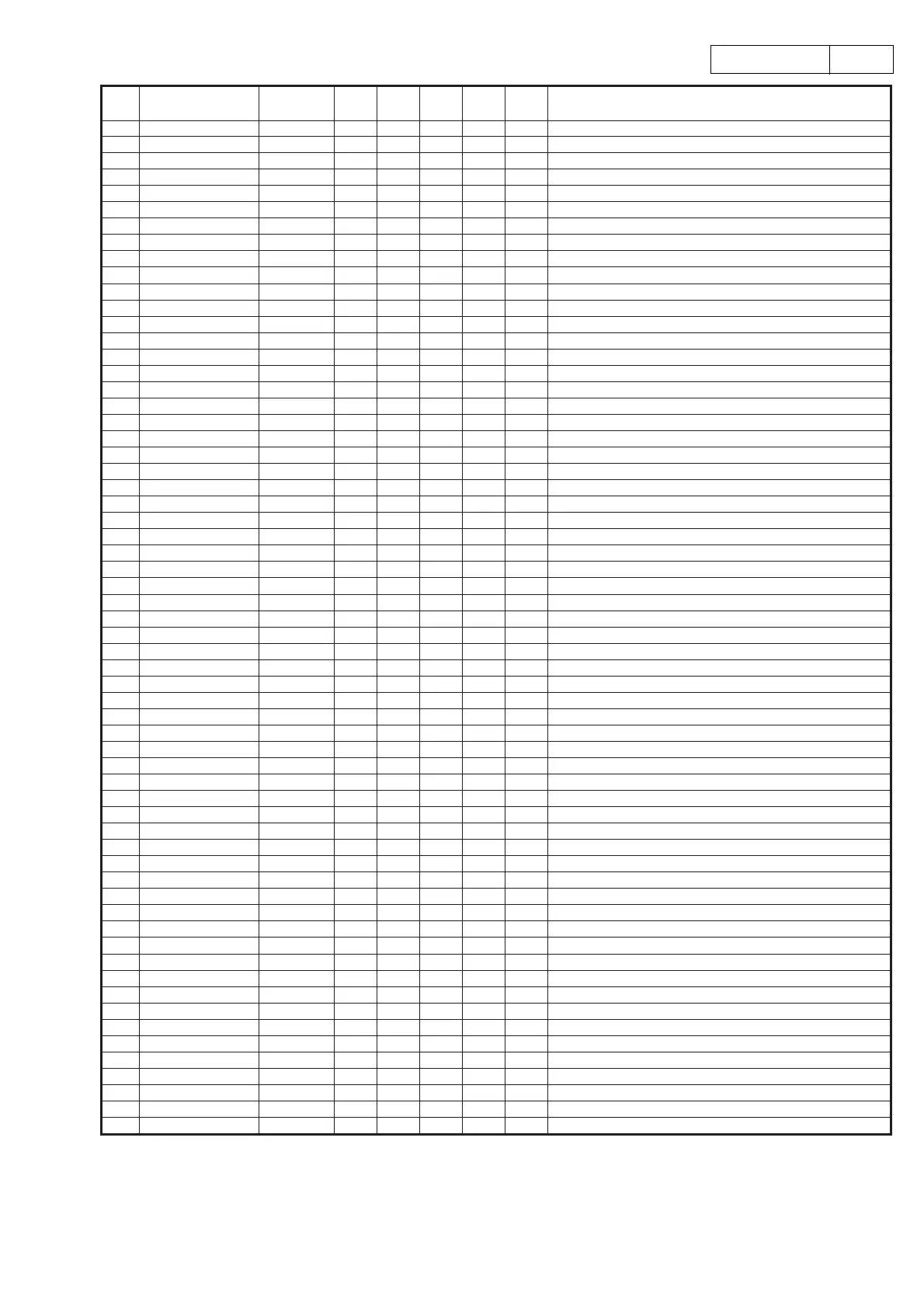

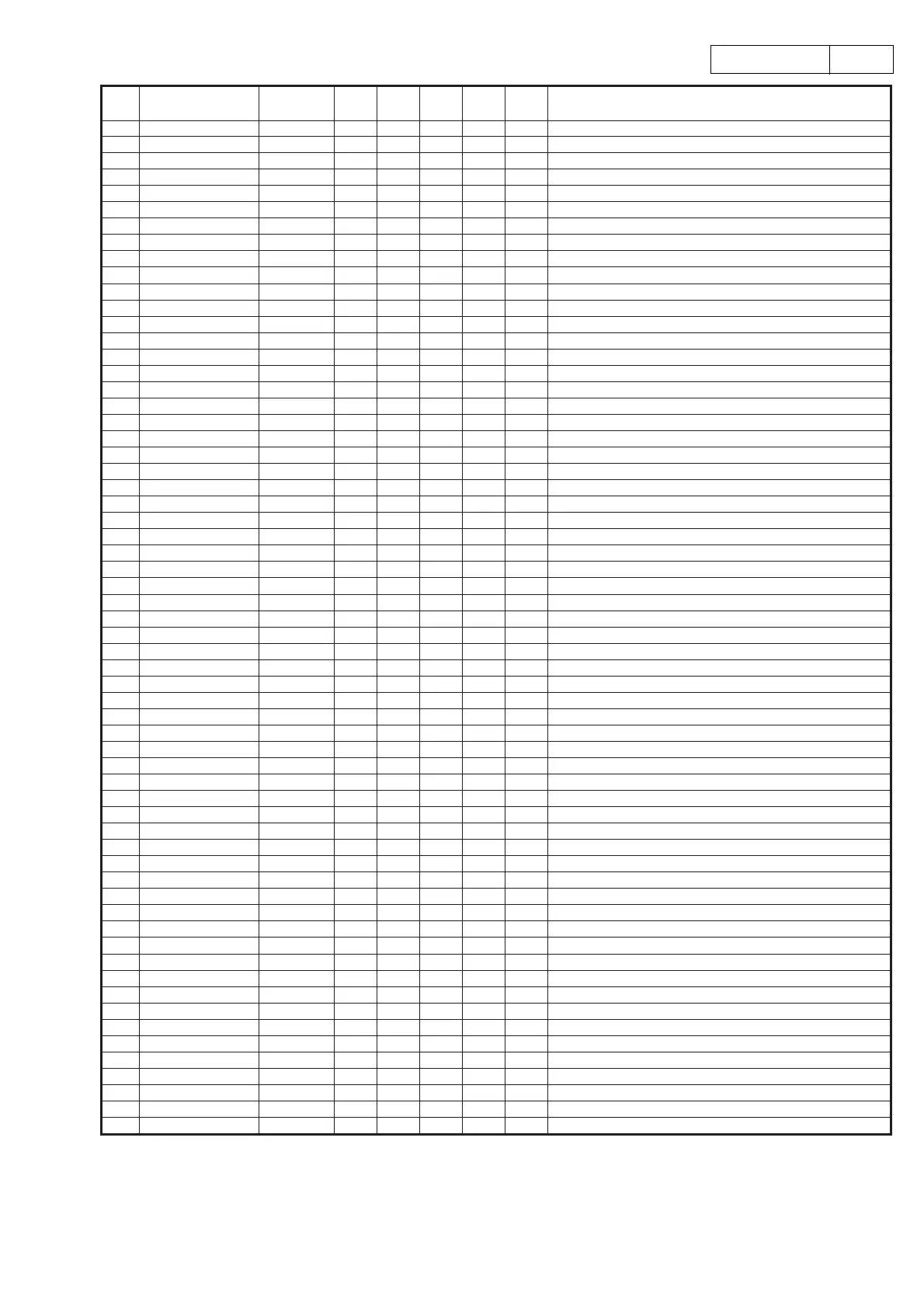

11

11DN-S5000

Function

I/O

Pin

No.

Pin Name

Symbol

DET Ext Ini Res

26 PC3 MUTE O — Pu H H Mute signal (H: Mute)

27 XI XI I — — — — Oscillation input

28 XO XO O — — — — Oscillation output

29 VDD VDD — — — — — Power (+3.3V)

30 OSCI OSCI I — — — — Oscillation input, 34.0MHz

31 OSCO OSCO O — — — — Oscillation output

32 VSS VSS — — — — — GND

33 P57,BOSC TEST

NMI

I—

Pu H —

P.W.B. check mode IN

Connect to Power

34 PC5,NMI I — —

——

35 RST_ RST_ I —

——

— µcom reset

36 PC0 YMCLK O —

—

H — Clock for SM5902(DOUT)/PCM1608(D/A) data

37 P76 MDO O — Pd — L PCM1608(D/A) input data

38 P60,IRQ0 DTIMA I — Pu H H Main playback clock input

39 P61,IRQ1 DTIMB I — Pu H H Monitor playback clock input

40 P62,IRQ2,TM10IOA TABLE I — (Pu) H H Clock pulse input for platter

41 P63,IRQ3,TM10IOA CLK4M I — — — — Clock pulse input for platter

42 P64,IRQ4 ATANS_ I — (Pu) — H ATAPI µcom serial interface

43 P65,IRQ5,TM12IOA DISCPA I — (Pu) H H Clock pulse input for scratch disc

44 P66,IRQ6 DISCDIR I — (Pu) H H Direction pulse input for scratch disc

Start pulse input for scratch disc

45 P67,IRQ7 DISCINT I — (Pu) H H

46 P70,TM13IOB DISCA I —

———

SCRATCH for DISC pulse A count input

47 P71 YMDATA O — — H — SM5902(DOUT)/PCM1608(D/A) output data

48 PD2,DMAACK0_ NRES_ O — Pd L L SM5902(DOUT)/PCM1608(D/A) reset signal

Clock invert pulse input for scratch disc

49 PD3,TM3IO DISCPA_ I — — —

50 VDD VDD — — — — — P

—

ower (+3.3V)

51 P77 ZSENCE2 I — — — — SM5902 µcom interface status for MONITOR

52 P72,TM14IOB DISCPB I — — — — SCRATCH for DISC pulse B count input

53 P73 YMLD1_ O — — H — SM5902(DOUT) chip select for MAIN

54 P74 YMLD2_ O — — H — SM5902(DOUT) chip select for MONITOR

55 P75,TM12IOB CLK4M I — — — — Clock pulse input for disc

56 PA0,SBI0 RXD1 I — (Pu) — H Data receive from PANEL

57 PA1,SBO0 TXD1 O — Pu H H Data send to PANEL (PU µcom specify)

58 PA2,SBT0 MCMD_ O — Pu H H ATAPI µcom serial interface (PU µcom specify)

59 PA3,SBI1 X'RXDOUT I — (Pd) — H Data receive from X'EFFECT OUT

60 PA4,SBO1 X'TXDOUT

ZSENCE1

O — Pu H H Data send to X'EFFECT OUT

61 PA5 I — — — — SM5902 µcom interface status for MAIN

62 PB0,SBI2 X’RXD IN I — (Pd) — H Data receive from X’EFFECT IN

63 PB1,SBO2 X’TXD IN O — Pu H H Data send to X’EFFECT IN

64 PB2 APRES_ O — Pd L L ATAPI µcom reset signal

65 PB3,SBI3 ATDATA I — (Pu) — H ATAPI µcom serial receive signal

66 PB4,SBO3 MDATA O — — H — ATAPI µcom serial send signal

67 PB5,SBT3 MCLK O — — H — ATAPI µcom serial send/receive clock

68 VDD VDD — — — — — Power (+3.3V)

69 VSS VSS — — — — — GND

70 AVSS AVSS — — — — — Analog ref. GND for A/D conversion, GND

71 Vref Vref — — — — — Analog ref. V for A/D conversion, GND

72 P80 DFLG2 I/O — Pu — H DSP gener al flag 2

73 P81 DFLG1 I/O — Pu — H DSP gener al flag 1

74 P82 DR_/W1 O — — H — DSP interf ace send/receive select signal

75 P83 DACK_ I — Pu H H DSP interf ace ACK

76 P84 DBSY_ I — Pu H H DSP interf ace busy signal

77 P85 DFLG0 I/O — Pu — H DSP gener al flag 0

78 P86 DREQ_ O — Pu H H

HH

DSP interf ace request signal

79 P87 FPLAY1 I — Main fader start PLAY input

80 PD4 FCUE1 I — (Pu) H H Main fader start CUE input

81 PD5 FPLAY2 I — (Pu)

(Pu)

H H Monitor fader start PLAY input

82 P90 FCUE2 I — H Monitor fader start CUE input

83 P91 RESERVE O — — L —

84 P92 PNLRST — — Pd L L Panel µcom reset signal (L:Reset)

85 P93 APOWER O — Pd L L Analog output voltage ON/OFF (L:OFF)

86 Vref+ Vref+ — — — — — Analog ref. V for A/D conversion, +3.3V

87 AVDD AVDD — — — — — Power (+3.3V)

H

(Pu)

Loading...

Loading...