47

S-102

TSD0

33

O Audio transmit serial data output 0.

SEL_PLL0 I Refer to the description and matrix for SEL_PLL2 pin 32.

TSD1

36

O Audio transmit serial data output 1.

SEL_PLL1 I Refer to the description and matrix for SEL_PLL2 pin 32.

TSD2 37 O Audio transmit serial data output 2. This pin must be pulled down to VSS via a

4.7-k: resistor for proper operation.

TSD3 38 O Audio transmit serial data output 3.

MCLK 39 I/O Audio master clock for audio DAC.

TBCK 40 I/O Audio transmit bit clock. TBCK is an input during reset and subsequently is

programmed as an output via the AUDIOXMT register (addr 0x2000D00Ch, bit 4).

SEL_PLL3

41

I Clock source select. Strapped to VCC or ground via 4.7-k: resistor; read only

during reset.

SPDIF_OUT O S/PDIF output.

SPDIF_IN 42 I S/PDIF input; (5V tolerant input).

RSD 45 I Audio receive serial data; (5V tolerant input).

RWS 46 I Audio receive frame sync; (5V tolerant input).

RBCK 47 I Audio receive bit clock; (5V tolerant input).

CAMIN3

48

I Camera YUV 3.

PIXIN3 I CCIR656 input pixel 3.

XIN 49 I 27-MHz crystal input.

XOUT 50 O 27-MHz crystal output.

AVEE 51 P Analog power for PLL.

AVSS 52 G Analog ground for PLL.

DMA[11:0] 53-58, 61-66 O DRAM address bus.

DCAS# 69 O DRAM column address strobe.

DOE#

70

O DRAM output enable.

DSCK_EN O DRAM clock enable.

DWE# 71 O DRAM write enable.

DRAS# 72 O DRAM row address strobe.

DMBS0 73 O DRAM bank select 0.

DMBS1 74 O DRAM bank select 1.

DB[15:0] 77-82, 85-90, 93-96 I/O DRAM data bus.

DCS[1:0]# 97,100 O DRAM chip select.

DQM 101 O Data input/output mask.

DSCK 102 O Output clock to DRAM.

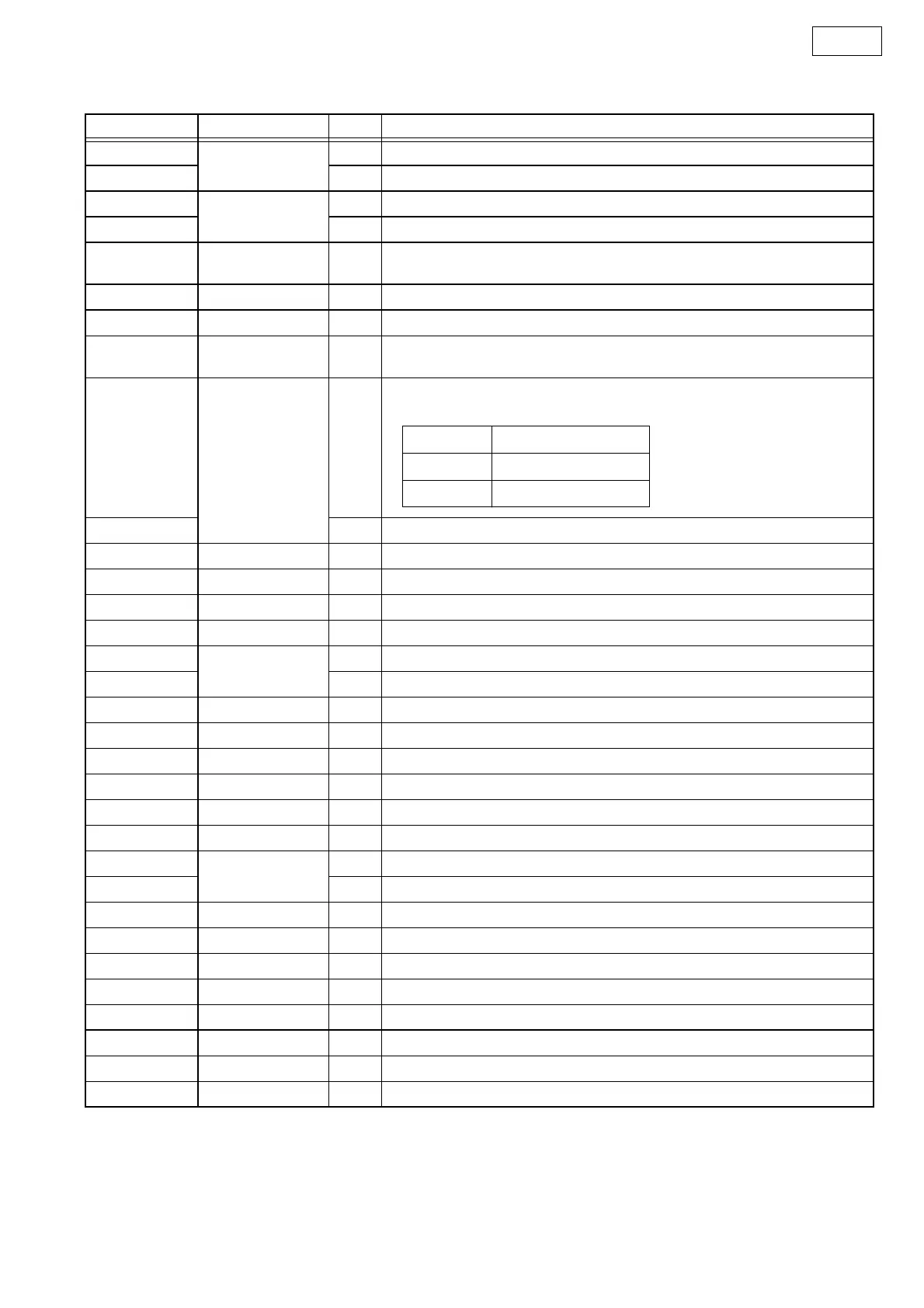

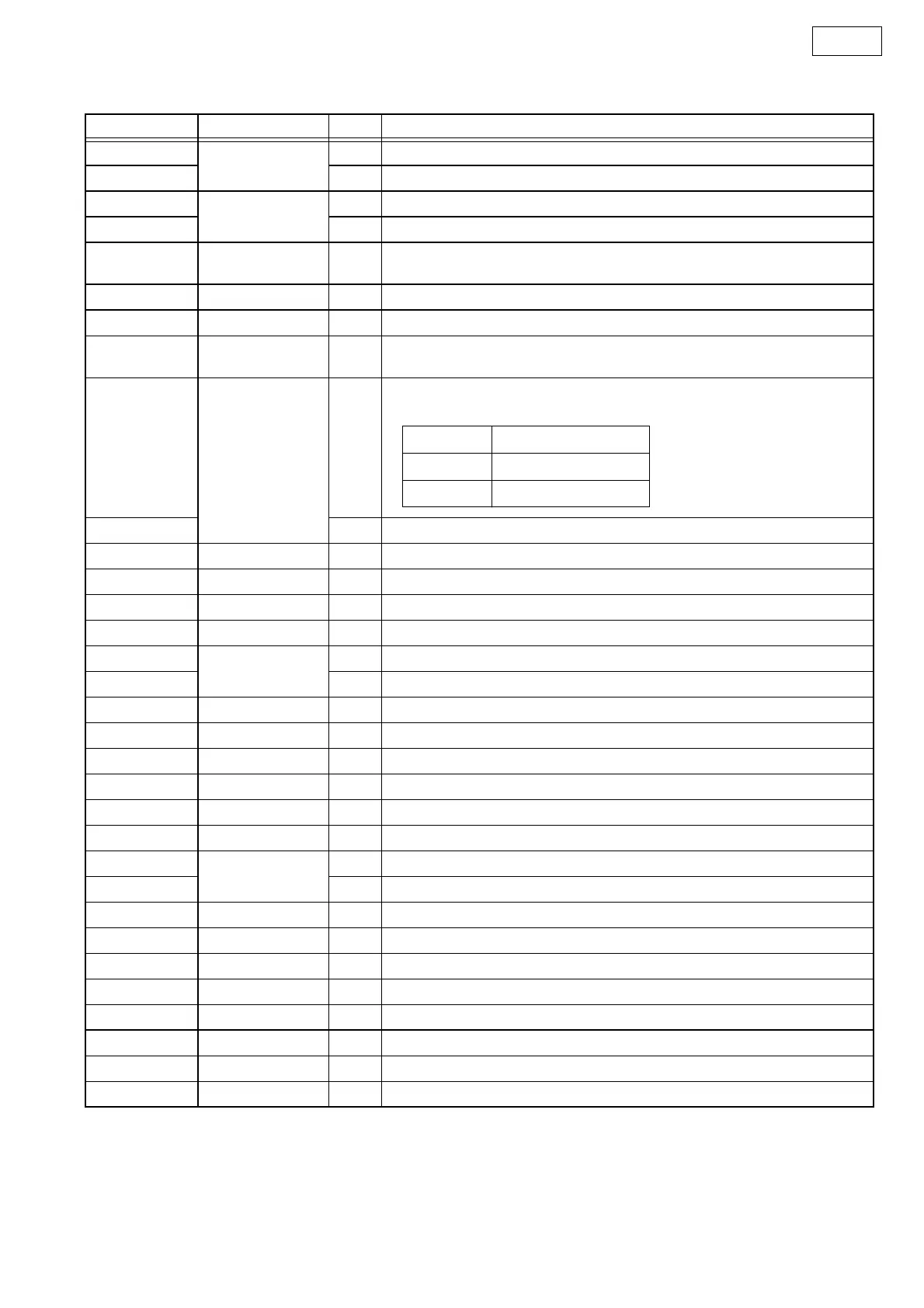

Name Pin Numbers I/O Definition

SEL_PLL3 Clock Source

0 Crystal oscillator

1 DCLK input

Loading...

Loading...