48

S-102

DCLK 105 I Clock input to PLL; (5V tolerant input).

UDAC

106

O Video DAC output.

F: CVBS/chroma signal for simultaneous mode.

Y: Luma component for YUV and Y/C processing.

C: Chrominance signal for Y/C processing.

U: Chrominance component signal for YUV mode.

V: Chrominance component signal for YUV mode.

YUV0 O YUV pixel 0 output data.

PIXOUT0 O CCIR656 output pixel 0.

VREF

107

I Internal voltage reference to video DAC. Bypass to ground with 0.1-PF capacitor.

YUV1 O YUV pixel 1 output data.

PIXOUT1 O CCIR656 output pixel 1.

CDAC

108

O Video DAC output. Refer to description and matrix for UDAC pin 106.

YUV2 O YUV pixel 2 output data.

PIXOUT2 O CCIR656 output pixel 2.

COMP

109

I Compensation input. Bypass to ADVEE with 0.1-PF capacitor.

YUV3 O YUV pixel 3 output data.

PIXOUT3 O CCIR656 output pixel 3.

RSET

110

I DAC current adjustment resistor input.

YUV4 O YUV pixel 4 output data.

PIXOUT4 O CCIR656 output pixel 4.

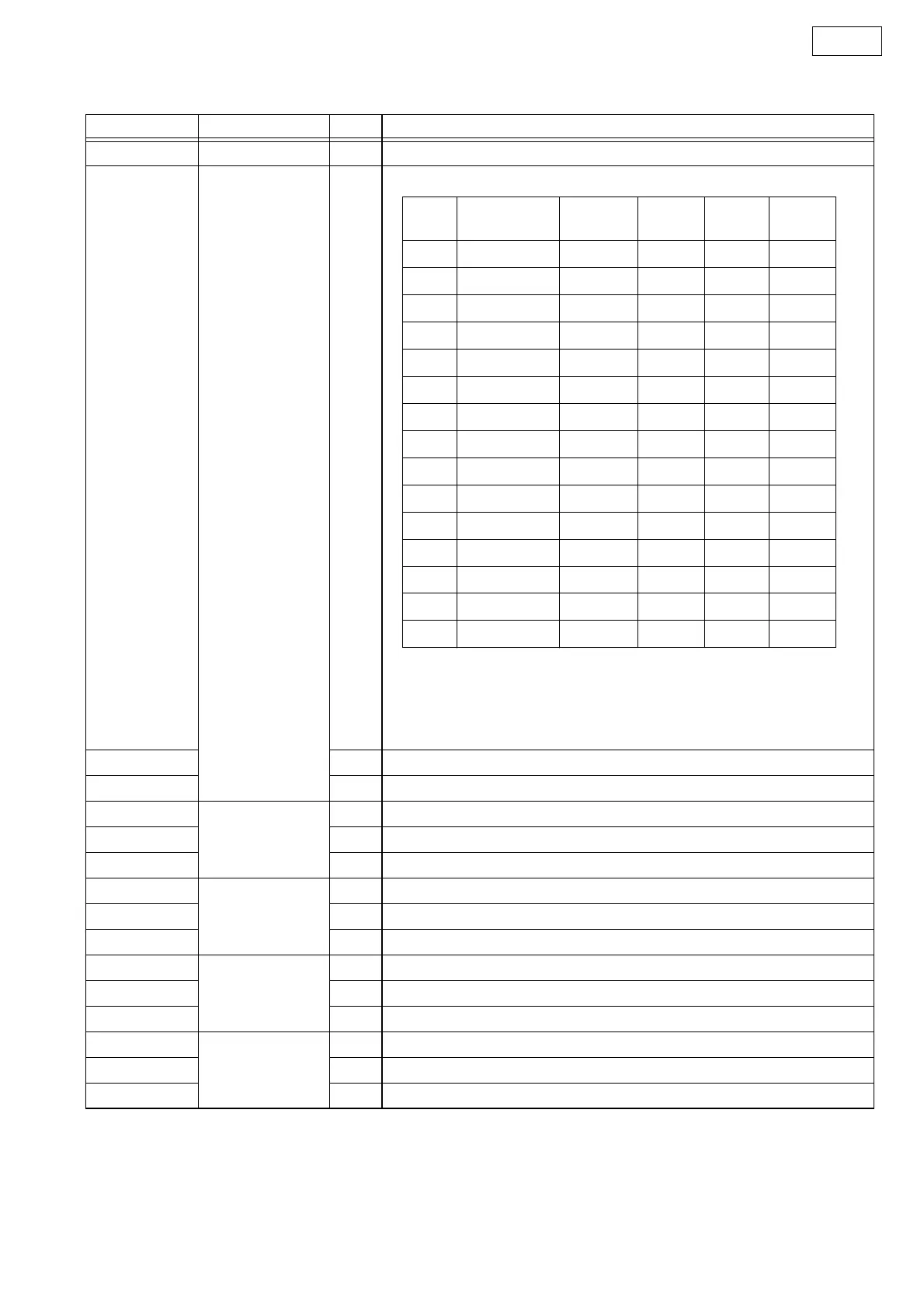

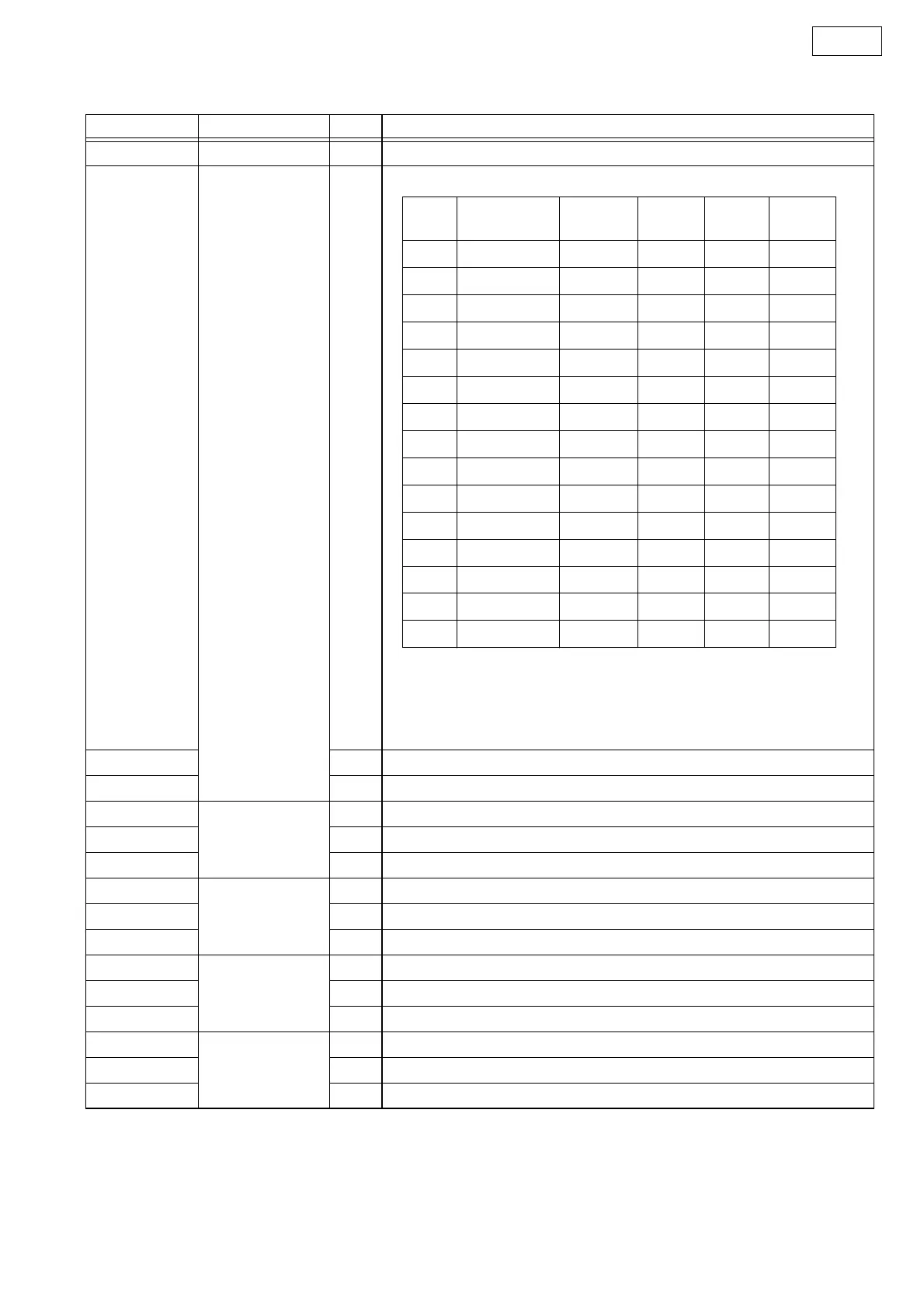

Name Pin Numbers I/O Definition

Value

F DAC

(pin 115)

V DAC

(pin 114)

Y DAC

(pin 113)

C DAC

(pin 108)

U DAC

(pin 106)

0 CVBS/Chroma CVBS1 Y C N/A

1 CVBS/Chroma CVBS1 Y C CVBS2

2 CVBS/Chroma N/A Y C N/A

3 CVBS/Chroma CVBS1 N/A N/A CVBS2

4 CVBS/Chroma CVBS1 N/A N/A N/A

5 CVBS/Chroma CVBS1 Y Pb Pr

6 CVBS/Chroma N/A Y Pb Pr

7 N/A SYNC G B R

8 CVBS/Chroma Chroma Y Pb Pr

9 CVBS CVBS1 G B R

10 CVBS CVBS1 G R B

11 N/A SYNC G R B

12 CVBS/Chroma N/A Y Pr Pb

13 CVBS/Chroma CVBS1 Y Pr Pb

14 Chroma Y G R B

Loading...

Loading...