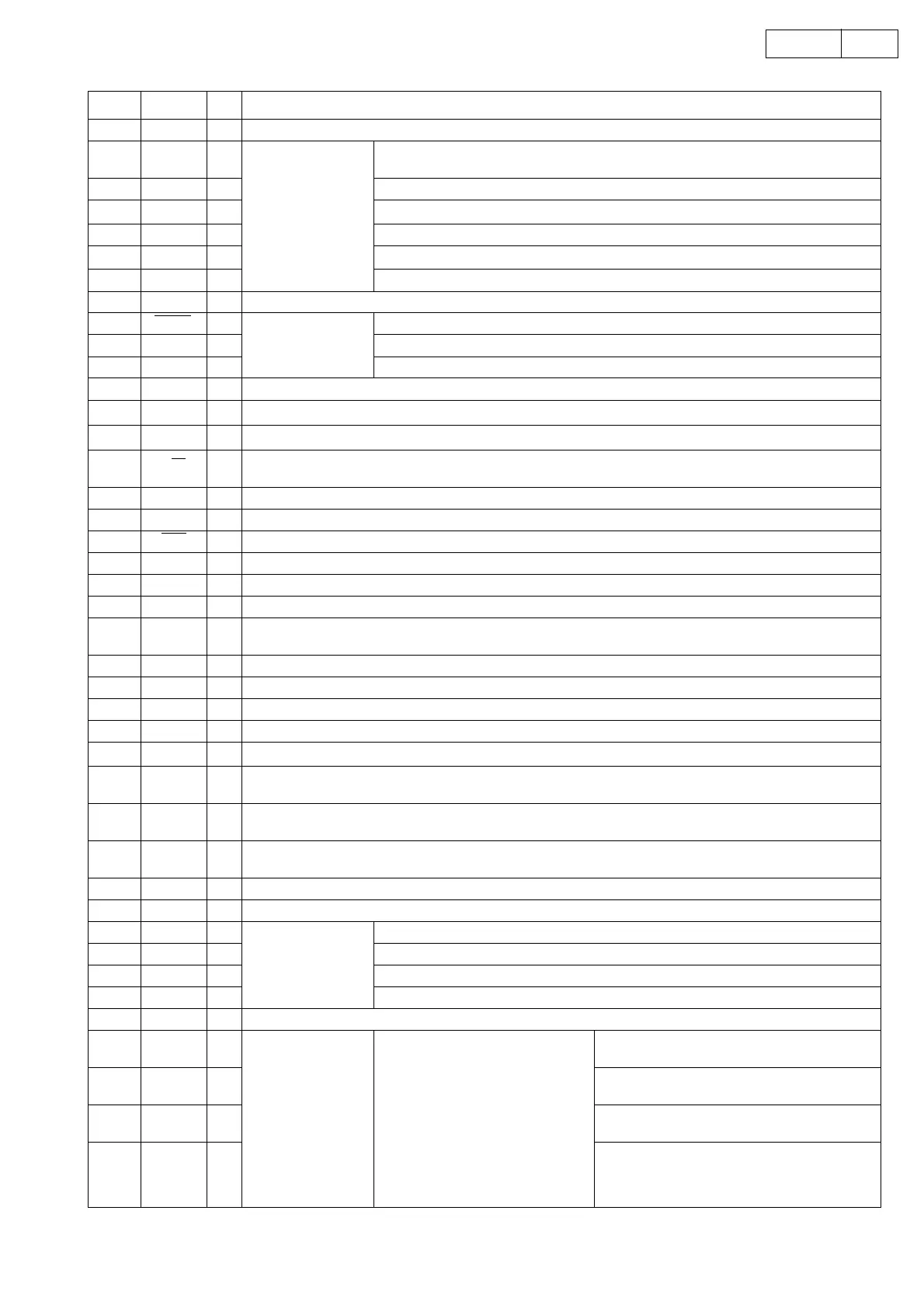

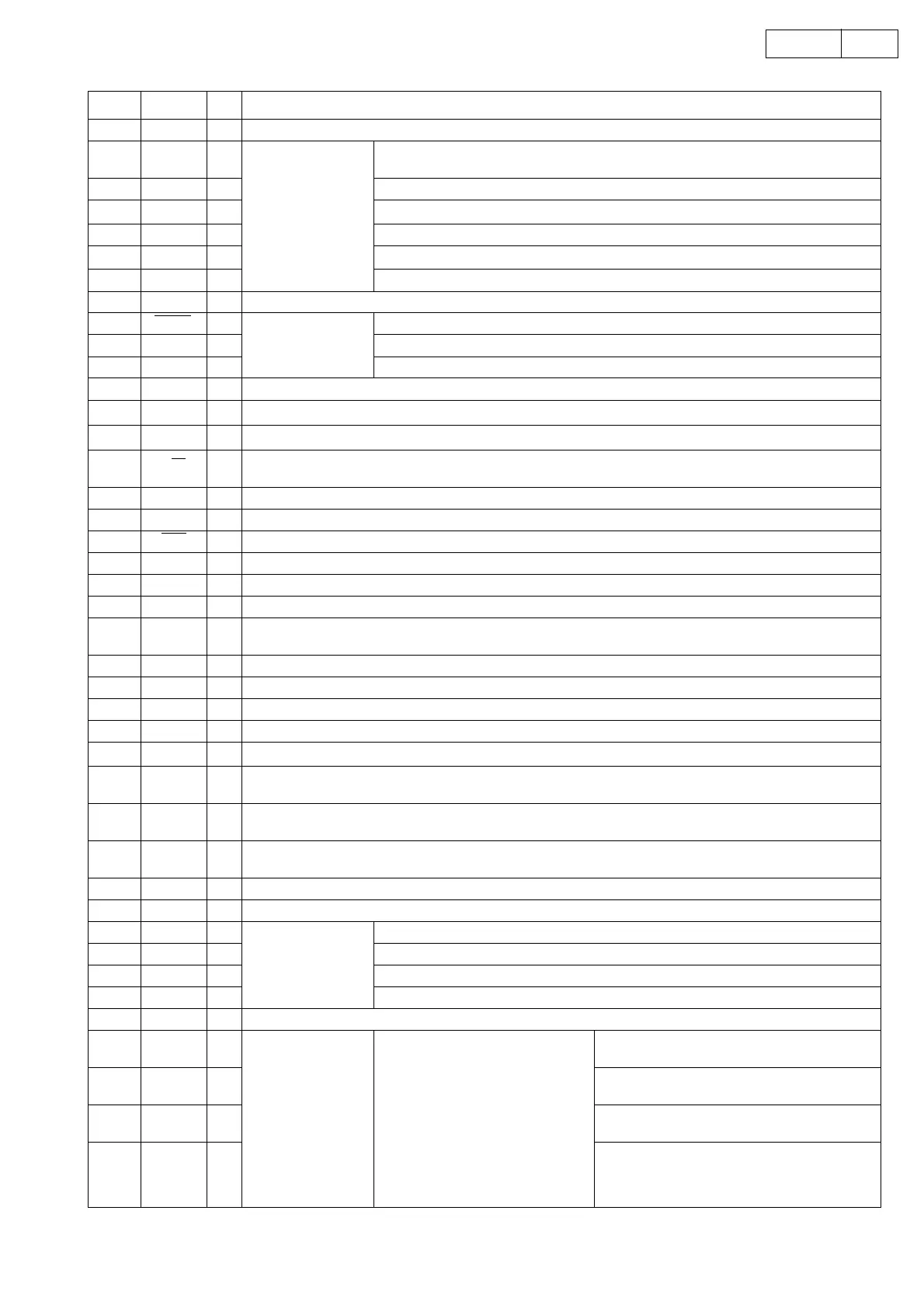

13

13UD-M31

LC78625E Terminal Function

Pin No. Symbol I/O Function

1 DEFI I Defect detection signal (DEF) input (This pin must be connected to 0 V if unused.)

2TAII

PLL pins

Test input. A pull-down resistor is built in. (This pin must be connected to 0 V in normal

operation.)

3 PDO O External VCO control phase comparator output

4

VV

SS

Internal VCO ground. (This pin must be connected to 0 V.) PLL pins

5 ISET AI PDO output current adjustment resistor connection

6

VV

DD

Internal VCO power supply.

7 FR AI VCO frequency range adjustment

8 VSS Digital system ground. (This pin must be connected to 0 V.)

9EFMOO

Slice level control

EFM signal inverted output

10 EFMO O EFM signal output

11 EFMIN I EFM signal input

12 TEST2 I Test input. A pull-down resistor is built in. This pin must be connected to 0 V in normal operation.

13

CLV

+

O Spindle servo control output. Acceleration when CLV+ is high, deceleration when CLV- is high.

14

CLV

-

O Three-value output is also possible when specified by microprocessor command.

15 V/P O

Rough servo/phase control automatic switching monitor output. Outputs a high level during rough servo and a low

level during phase control.

16 FOCS O Focus servo on/off output. Focus servo is on when the output is low.

17 FST O Focus start pulse output. This is an open-drain output.

18 FZD I Focus error zero cross signal input. (This pin must be connected to 0 V if unused.)

19 HFL I Track detection signal input. This is a Schmitt input.

20 TES I Tracking error signal input. This is a Schmitt input

21 PCK O EFM data playback clock monitor. Outputs 4.3218 MHz when the phase is locked.

22 FSEQ O

Synchronization signal detection output. Outputs a high level when the synchronization signal detected from the

EFM signal and the internally generated synchronization signal agree.

23 TOFF O Tracking off output

24 TGL O Tracking gain switching output. Increase the gain when low.

25 THLD O Tracking hold output

26 TEST3 I Test input. A pull-down resistor is built in. (This pin must be connected to 0 V.)

27

V

DD

Digital system power supply.

28

JP

+

O

Track jump output. A high level output from JP+ indicates acceleration during an outward jump or deceleration dur-

ing an inward jump.

29

JP

-

O

A high level output from JP- indicates acceleration during an inward jump or deceleration during an outward

jump.Three-value output is also possible when specified by microprocessor command.

30 DEMO I

Sound output function input used for end product adjustment manufacturing steps. A pull-down resistor is built in.

(This pin must be connected to 0 V.)

31 TEST4 I Test input. A pull-down resistor is built in. (This pin must be connected to 0 V.)

32 EMPH O De-emphasis monitor pin. A high level indicates playback of a de-emphasis disk.

33 LRCKO O

Digital filter outputs

Word clock output

34 DFORO O Right channel data output

35 DFOLO O Left channel data output

36 DACKO O Bit clock output

37 TST10 O Test output. Leave open. (Normally outputs a low level.)

38

ASDACK

/P0

I/O

When antishock

mode is not

used,these pins are

used as general pur-

pose I/O ports (P0 to

P3). They must either

be set to input mode

and connected to 0 V,

or set to output mode

and left open, if

unused.

The antishock inputs in antishock

mode.

Bit clock input

39

ASDFIN/

P1

I/O Left and right channel data input

40

ASDEPC

/P2

I/O

Sets the built-in de-emphasis filter on or off.(High:

on, low: off)

41

ASLRCK/

P3

I/O L/R clock input

Loading...

Loading...