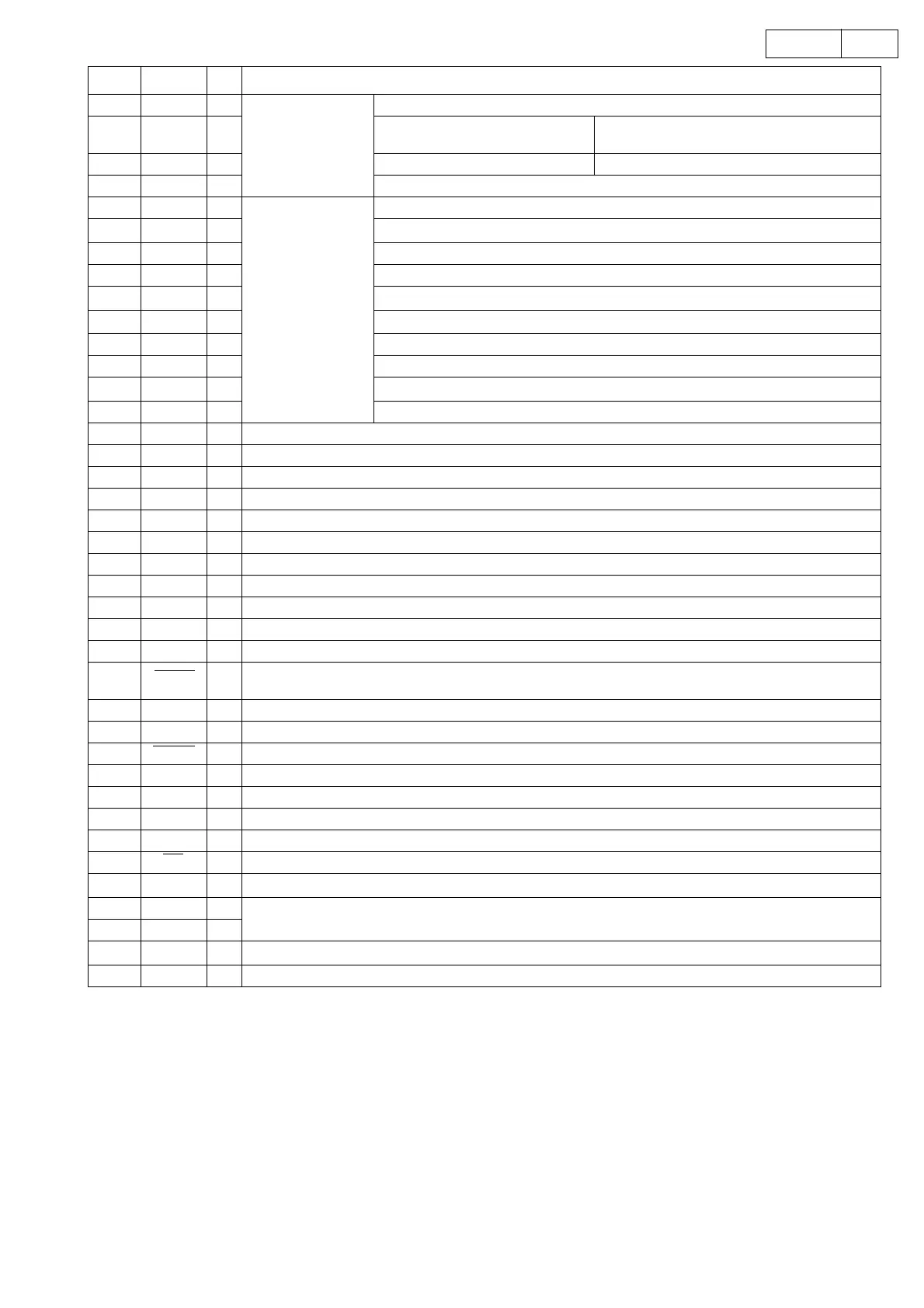

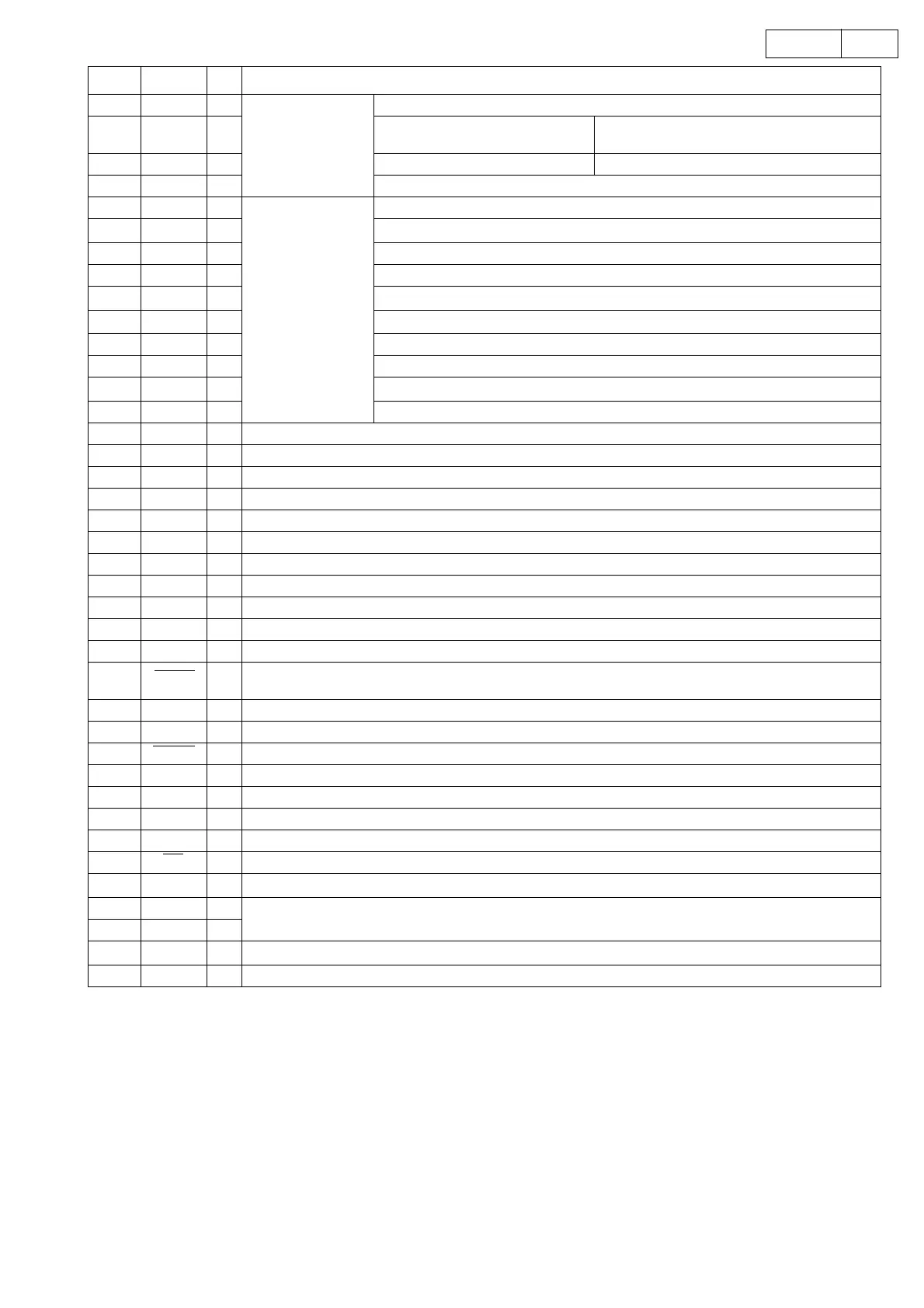

14

14UD-M31

Note: All power-supply pins (V

DD

, VV

DD

, LV

DD

, RV

DD

, and XV

DD

) must be connected to the same potential.

42 LRSY O

ROMXA application

output signals

L/R clock output

43 CK2 O Bit clock output(after reset)

Inverted polarity clock output(during CK2CON

mode)

44 ROMXA O Interpolation data output(after reset) ROM data output (during ROMXA mode)

45 C2F O C2 flag output

46 MUTEL O

One-bit D/A converter

signals

Left channel mute output

47

LV

DD

Left channel power supply

48 LCHP O Left channel P output

49 LCHN O Left channel N output

50

LV

SS

Left channel ground. Must be connected to 0 V.

51

RV

SS

Right channel ground. Must be connected to 0 V.

52 RCHN O Right channel N output

53 RCHP O Right channel P output

54

RV

DD

Right channel power supply

55 MUTER O Right channel mute output

56 DOUT O Digital output

57 SBSY O Subcode block synchronization signal output

58 EFLG O C1, C2, single and double error correction monitor pin

59 PW O Subcode P, Q, R, S, T, U and W output

60 SFSY O Subcode frame synchronization signal output. This signal falls when the subcodes are in the standby state.

61 SBCK I Subcode readout clock input. This is a Schmitt input. (This pin must be connected to 0 V if unused.)

62 FSX O Output for the 7.35 kHz synchronization signal divided from the crystal oscillator

63 WRQ O Subcode Q output standby output

64 RWC I Read/write control input. This is a Schmitt input.

65 SQOUT O Subcode Q output

66 COIN I Command input from the control microprocessor

67 CQCK I

Input for the command input acquisition clock or the SQOUT pin subcode readout clock input. This is a Schmitt

input.

68 RES I Reset input. This pin must be set low briefly after power is first applied.

69 TST11 O Test output. Leave open. (Normally outputs a low level.)

70 LASER O Laser on/off output. Controlled by serial data commands from the control microprocessor.

71 16M O 16.9344 MHz output

72 4.2M O 4.2336 MHz output

73 CONT O Supplementary control output. Controlled by serial data commands from the control microprocessor.

74 TEST5 I Test input. A pull-down resistor is built in. (This pin must be connected to 0 V.)

75 CS I Chip select input. A pull-down resistor is built in. This pin must be connected to 0 V if unused.

76

XV

SS

Crystal oscillator ground. Must be connected to 0 V.

77 XIN I

Connections for a 16.9344 MHz crystal oscillator

78 XOUT O

79

XV

DD

Crystal oscillator power supply

80 TEST1 I Test input. A pull-down resistor is built in. (This pin must be connected to 0 V.)

Pin No. Symbol I/O Function

Loading...

Loading...