28

22” TFT TV Service Manual

• Up to 2.38 Gbps throughput

• Up to 297.5 Megabytes/sec bandwidth

• 345 mV (typ) swing LVDS devices for low EMI

• PLL requires no external components

• Compatible with TIA/EIA-644 LVDS standard

• Low profile 56-lead or 48-lead TSSOP package

• DS90C385 also available in a 64 ball, 0.8mm fine pitch ball grid array (FBGA) package

11.21.3. Pin Descriptions

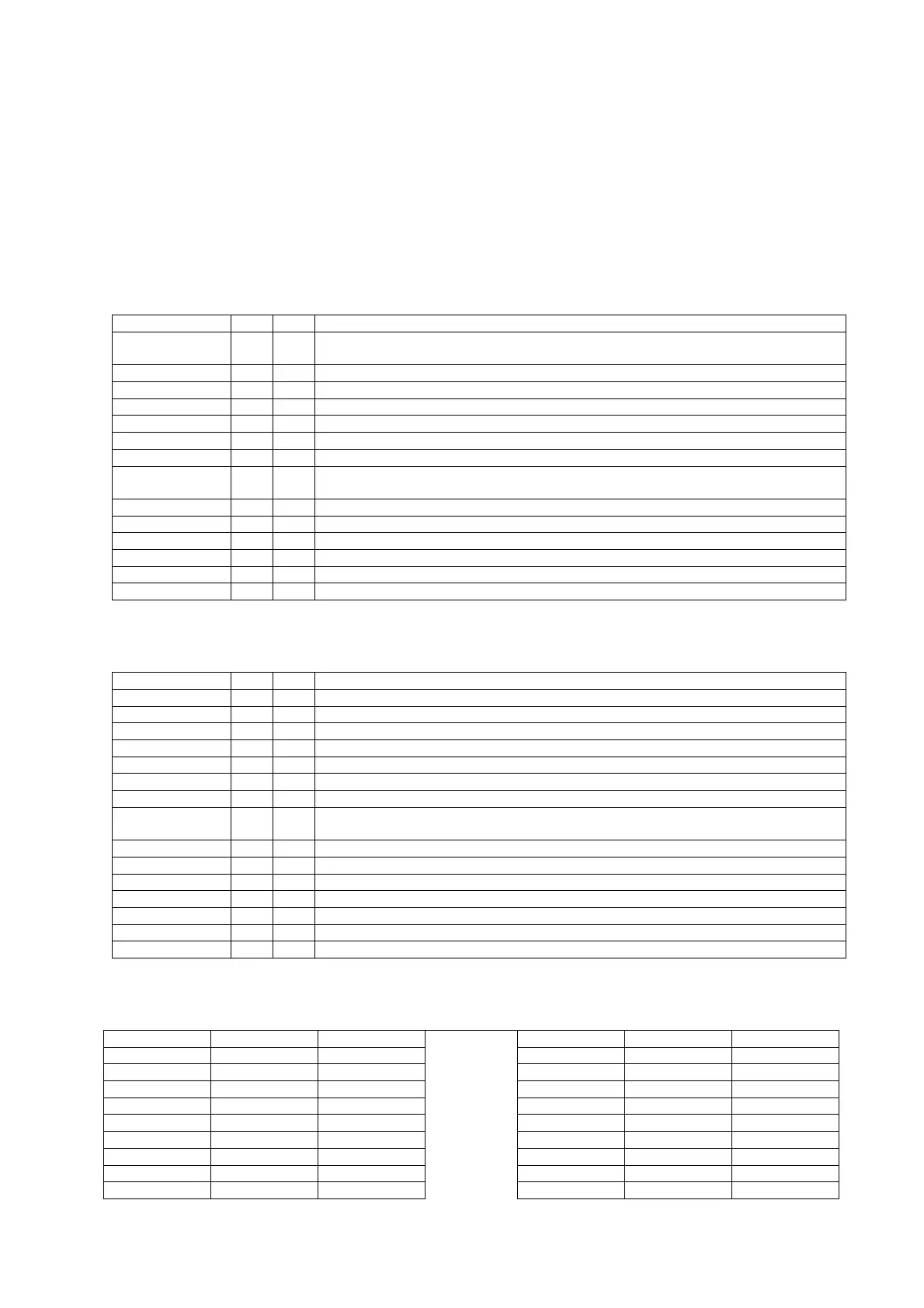

DS90C385 MTD56 (TSSOP) Package Pin Description — FPD Link Transmitter

Pin name I/O No. Description

TxIN I 28 TTL level input. This includes: 8 Red, 8 Green, 8 Blue, and 4 control lines -FPLINE,

FPFRAME and DRDY (also referred to as HSYNC, VSYNC, Data Enable).

TxOUT+ O 4 Positive LVDS differentiaI data output.

TxOUT- O 4 Negative LVDS differential data output.

TxCLKIN I 1 TTL Ievel clock input. Pin name TxCLK IN.

R_FB I 1 Programmable strobe select

TxCLK OUT+ O 1 Positive LVDS differential clock output.

TxCLK OUT- O 1 Negative LVDS differential clock output.

PWR DOWN I 1 TTL level input. Assertion (low input) TRI-STATES the outputs, ensuring low

current at power down.

V

CC

I 3 Power supply pins for TTL inputs.

GND I 4 Ground pins for TTL inputs.

PLL V

CC

I 1 Power supply pin for PLL.

PLL GND I 2 Ground pins for PLL.

LVDS V

CC

I 1 Power supply pin for LVDS outputs.

LVDS GND I 3 Ground pins for LVDS outputs.

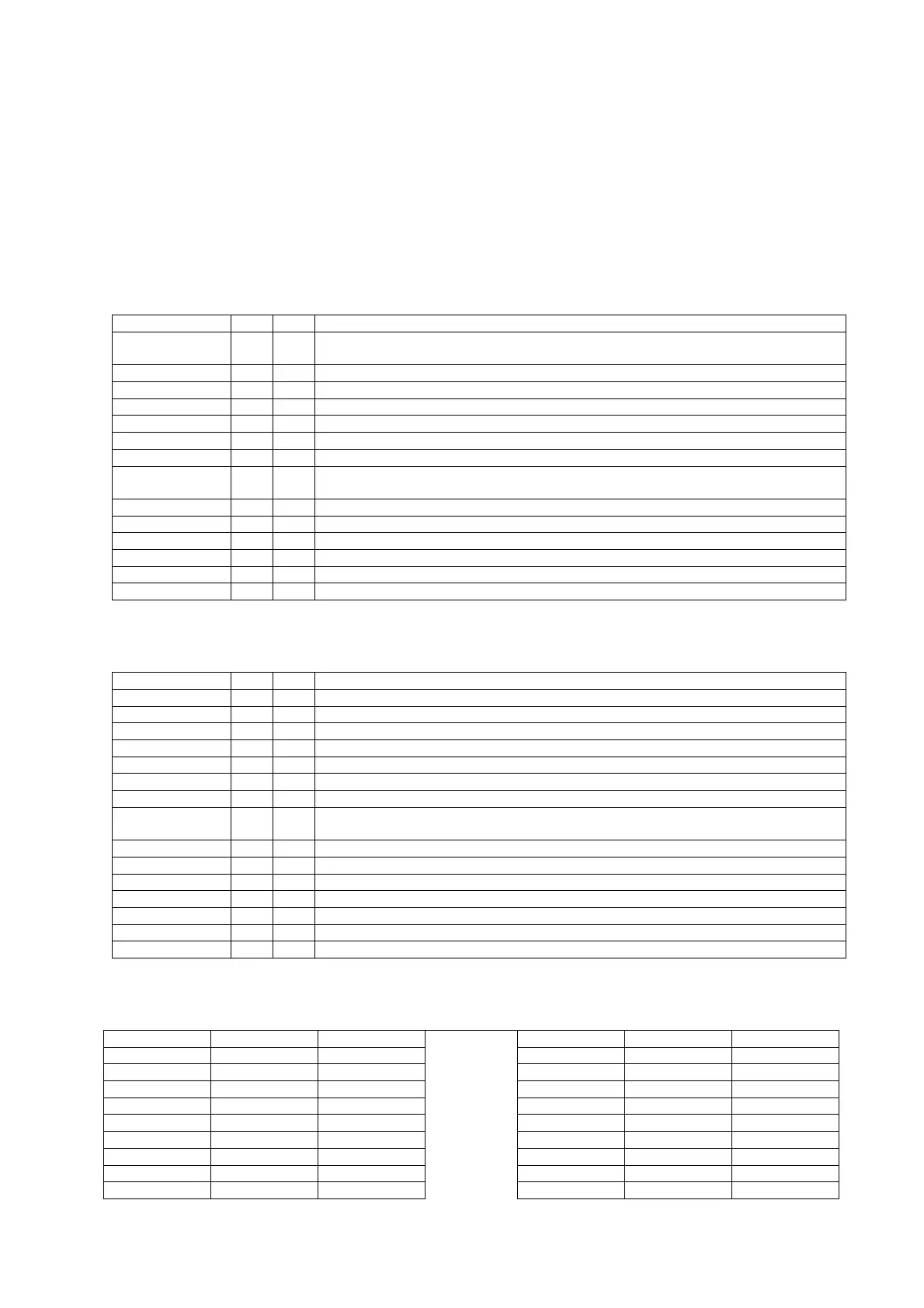

DS90C385SLC SLC64A (FBGA) Package Pin Summary — FPD Link Transmitter

Pin name I/O No. Description

TxIN I 28 TTL level input.

TxOUT+ O 4 Positive LVDS differentiaI data output.

TxOUT- O 4 Negative LVDS differential data output.

TxCLKIN I 1 TTL Ievel clock input. The rising edge acts as data strobe. Pin name TxCLK IN.

R_FB I 1 Programmable strobe select. HIGH = rising edge, LOW = falling edge.

TxCLK OUT+ O 1 Positive LVDS differential clock output.

TxCLK OUT- O 1 Negative LVDS differential clock output.

PWR DOWN I 1 TTL level input. Assertion (low input) TRI-STATES the outputs, ensuring low

current at power down.

V

CC

I 3 Power supply pins for TTL inputs.

GND I 4 Ground pins for TTL inputs.

PLL V

CC

I 1 Power supply pin for PLL.

PLL GND I 2 Ground pins for PLL.

LVDS V

CC

I 1 Power supply pin for LVDS outputs.

LVDS GND I 3 Ground pins for LVDS outputs.

NC 6 Pins not connected.

DS90C385SLC SLC64A (FBGA) Package Pin Description — FPD Link Transmitter

Pin Pin Name Type Pin Pin Name Type

A1 TxIN27 I D3 GND G

A2 TxOUT0- O E4 GND G

A3 TxOUT0+ O E8 GND G

A4 LVDS VCC P G1 GND G

A5 LVDS VCC P G6 GND G

A6 TxCLKOUT- O B3 LVDS GND G

A7 TxCLKOUT+ O B4 LVDS GND G

A8 TxOUT3+ O B7 LVDS GND G

B1 TxIN1 I D5 LVDS GND G

Loading...

Loading...