Hardware options installation 55

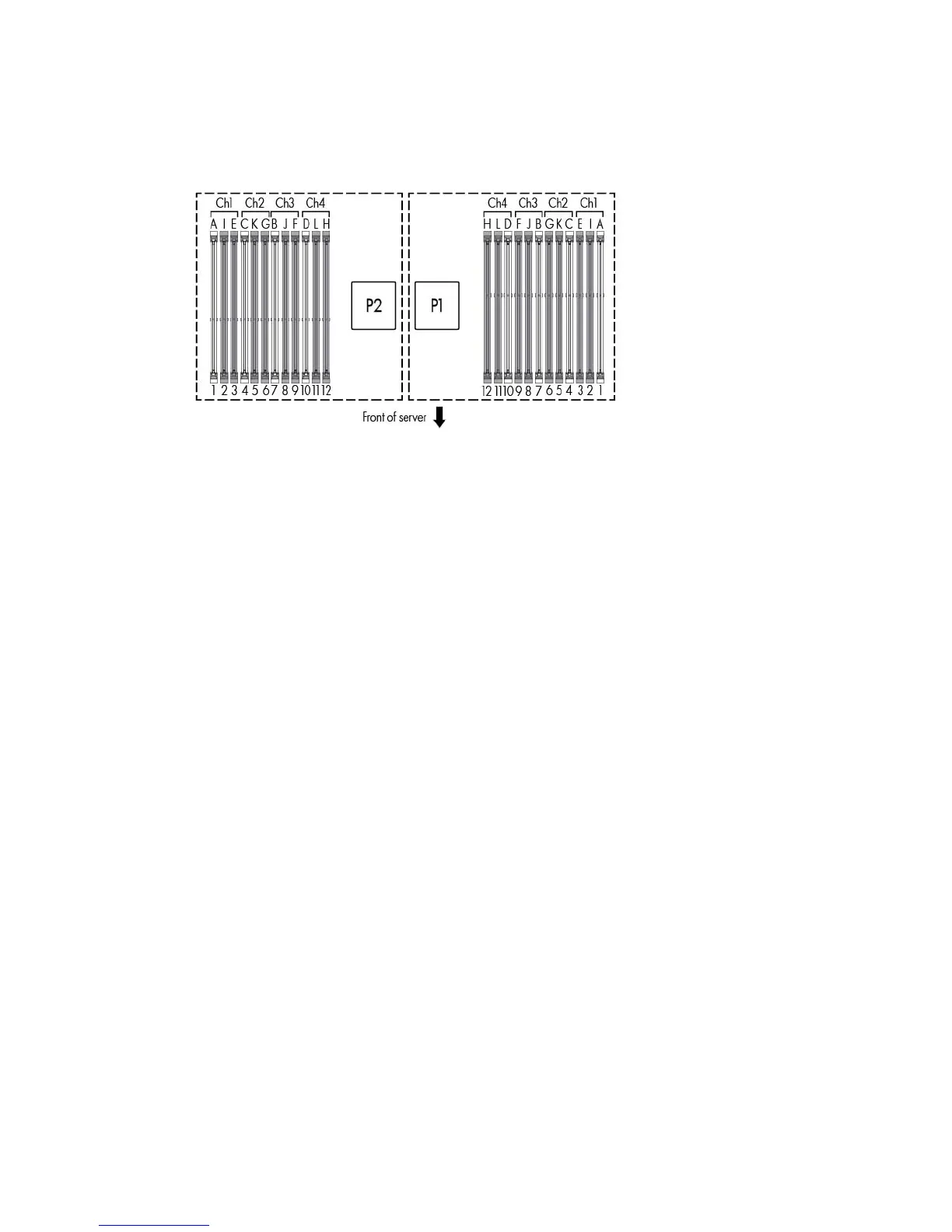

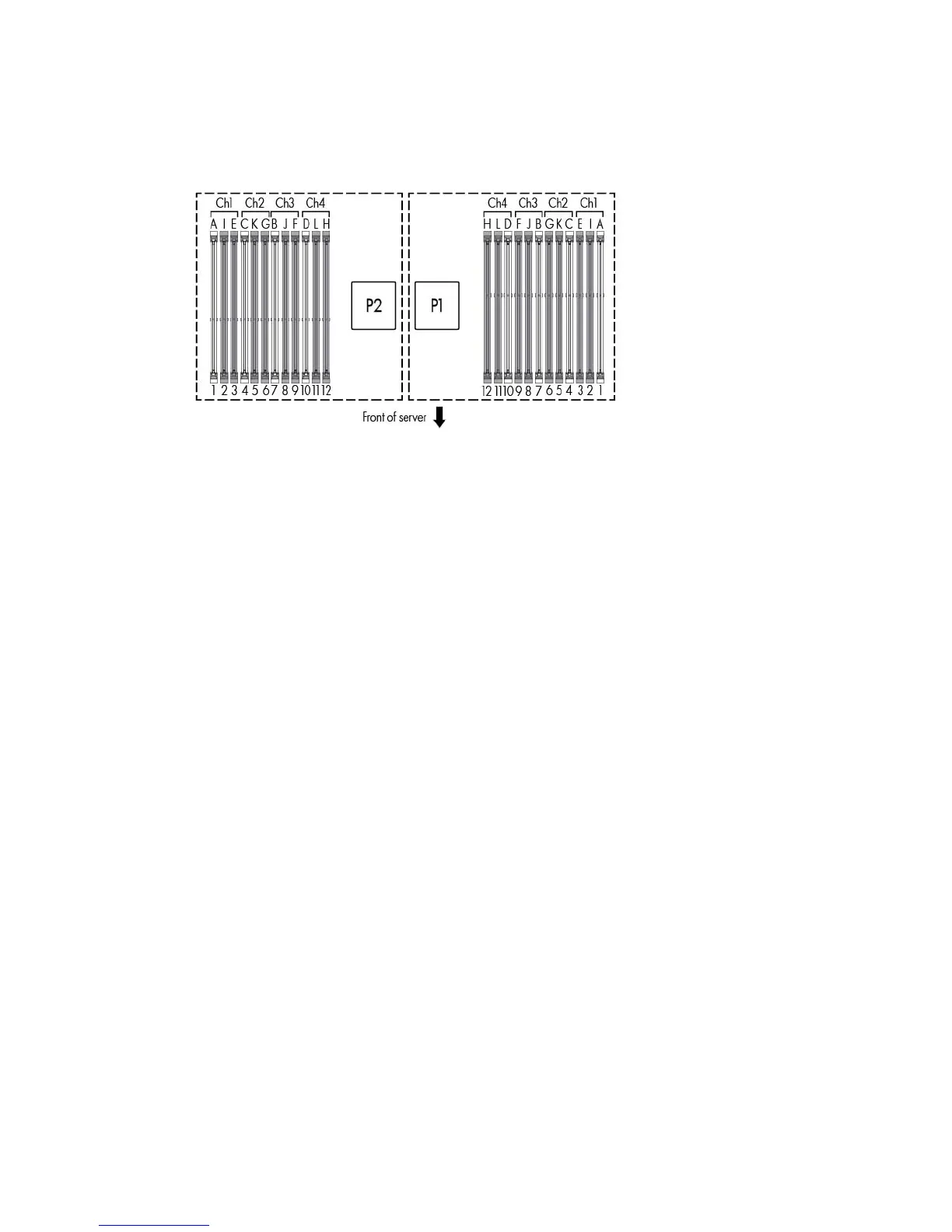

Memory subsystem architecture

The memory subsystem in this server is divided into channels. Each processor supports four channels, and

each channel supports three DIMM slots, as illustrated.

This multi-channel architecture provides enhanced performance in Advanced ECC mode. This architecture

also enables Online Spare Memory modes.

DIMM slots in this server are identified by number and by letter:

• Letters identify the population order.

• Slot numbers indicate the DIMM slot ID for spare replacement.

Population order

For memory configurations with a single processor or multiple processors, populate the DIMM slots in the

following order:

• LRDIMM: Sequentially in alphabetical order (A through L)

• RDIMM: Sequentially in alphabetical order (A through L)

After installing the DIMMs, use RBSU to configure Advanced ECC, or online spare memory support.

Single-, dual-, and quad-rank DIMMs

To understand and configure memory protection modes properly, an understanding of single-, dual-, and

quad-rank DIMMs is helpful. Some DIMM configuration requirements are based on these classifications.

A single-rank DIMM has one set of memory chips that is accessed while writing to or reading from the

memory. A dual-rank DIMM is similar to having two single-rank DIMMs on the same module, with only one

rank accessible at a time. A quad-rank DIMM is, effectively, two dual-rank DIMMs on the same module. Only

one rank is accessible at a time. The server memory control subsystem selects the proper rank within the

DIMM when writing to or reading from the DIMM.

Dual- and quad-rank DIMMs provide the greatest capacity with the existing memory technology. For

example, if current DRAM technology supports 8-GB single-rank DIMMs, a dual-rank DIMM would be 16

GB, and a quad-rank DIMM would be 32 GB.

LRDIMMs are labeled as quad-rank DIMMs; however, they function more like dual-rank DIMMs. There are

four ranks of DRAM on the DIMM, but the LRDIMM buffer creates an abstraction that allows the DIMM to

Loading...

Loading...