4-3-2

UHFPLL CIRCUIT (1F UNIT)

The oscillated signal at the VCO circuit (DUAL VCO

board

Q301, Q302,

D301)

is amplified at a buffer-amplifier

(Q306)

and is

again amplified at another buffer-amplifier

(Q352).

The

amplified signal is applied to the PLL IC

(IC851

pin

19),

and

then divided by serial data from the

CPU. It is the

phase-detected

with

the

divided reference

frequency and

the phase difference is output as pulses.

The output signals

from

IC851

(pin

13)

are converted to

DC

voltages (lock voltage) by the loop filter (R866,

C862)

and

are

then fed back to the UHF VCO circuit

to stabilize the

VCO

frequency.

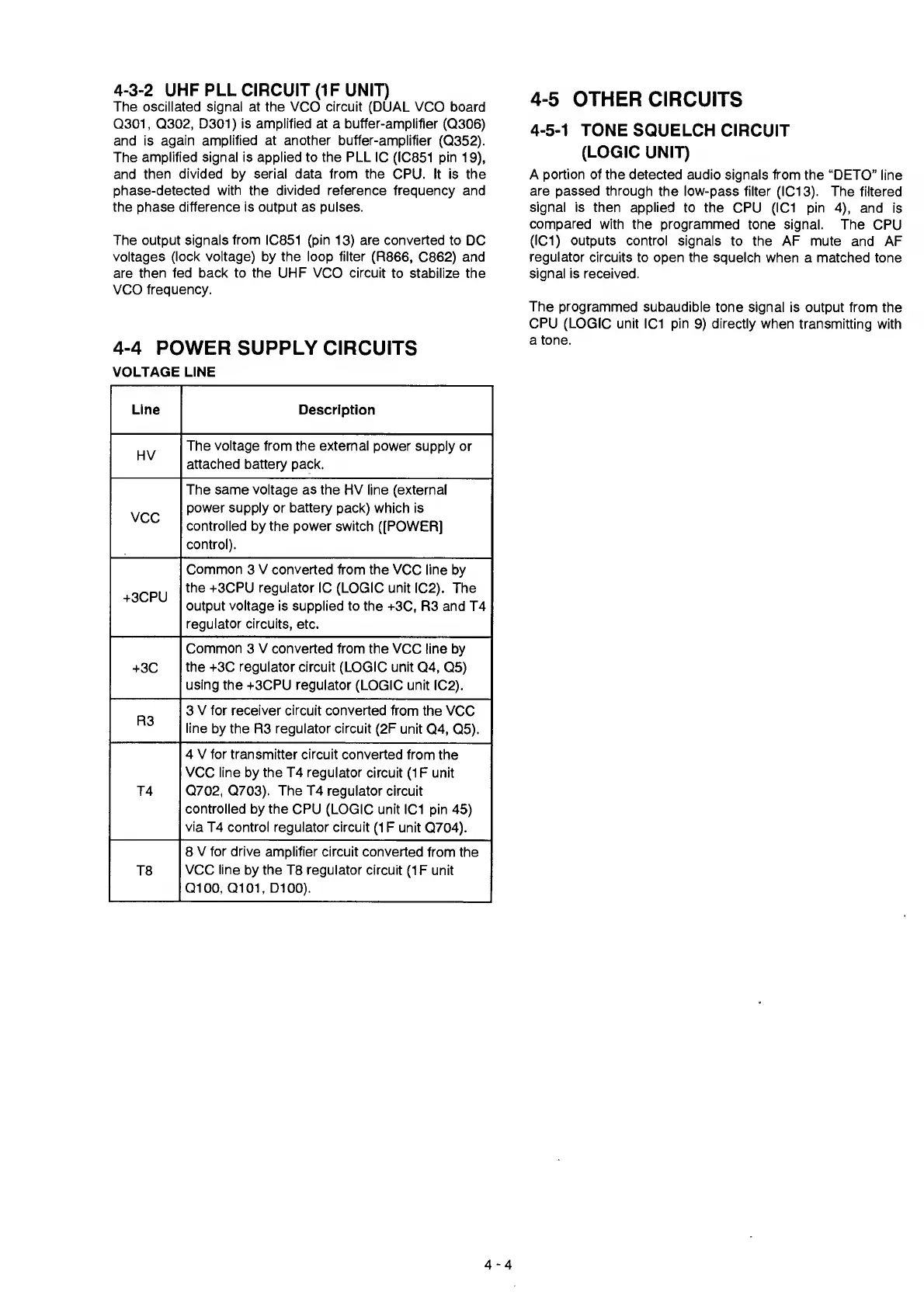

4-4

POWER SUPPLY CIRCUITS

VOLTAGE

LINE

Line Description

HV

The

voltage

from the external power

supply or

attached battery pack.

VCC

The same voltage as

the HV line (external

power supply or battery

pack) which is

controlled by the power switch

([POWER]

control).

+3CPU

Common

3 V

converted

from the

VCC line by

the +3CPU regulator

IC (LOGIC

unit

IC2).

The

output voltage

is supplied

to the

+3C,

R3

and

T4

regulator circuits,

etc.

+3C

Common

3

V converted

from the VCC

line by

the

+3C

regulator circuit

(LOGIC unit

Q4,

Q5)

using the +3CPU regulator

(LOGIC unit

IC2).

R3

3

V for receiver circuit converted

from

the VCC

line

by

the

R3 regulator circuit (2F

unit

04, 05).

T4

4 V for transmitter circuit

converted from

the

VCC line by the T4 regulator

circuit (1 F unit

0702, 0703).

The T4

regulator circuit

controlled by the CPU

(LOGIC unit IC1 pin

45)

via

T4

control

regulator circuit

(1 F unit

0704).

T8

8

V for drive amplifier

circuit converted

from the

VCC line by

the T8 regulator circuit

(1 F unit

01

00,

01

01,

D100).

4-5

OTHER CIRCUITS

4-5-1

TONE SQUELCH CIRCUIT

(LOGIC

UNIT)

A

portion

of the detected audio signals from

the “DETO”

line

are passed through

the

low-pass

filter (IC13). The

filtered

signal is then applied

to the CPU (IC1 pin

4),

and is

compared

with the programmed

tone signal. The

CPU

(IC1) outputs control signals

to the AF mute

and AF

regulator

circuits to open the squelch

when a matched tone

signal is received.

The programmed

subaudible

tone signal is output from

the

CPU

(LOGIC unit IC1 pin

9)

directly when

transmitting with

a tone.

4-4

Loading...

Loading...