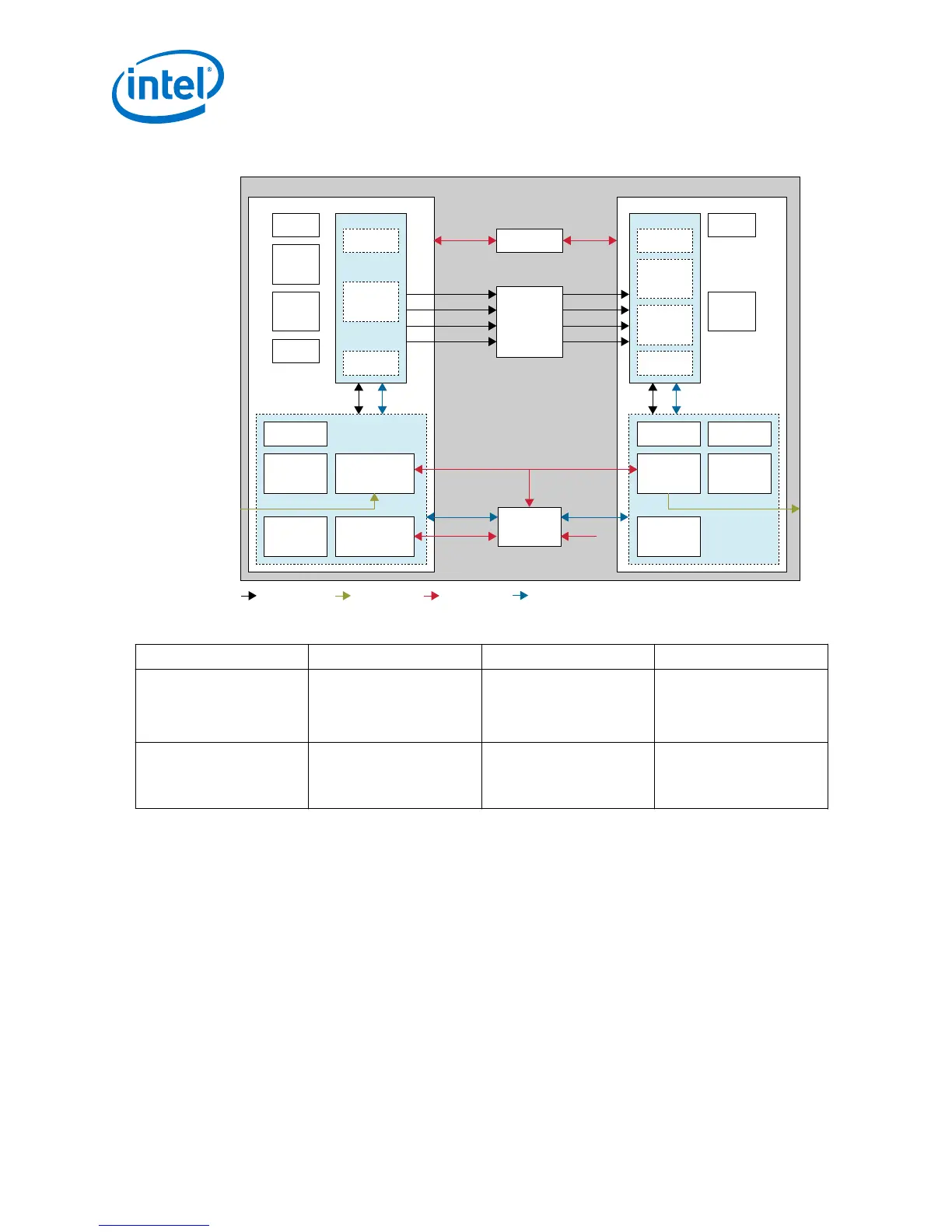

Figure 5. HDMI RX-TX Retransmit

I

2

C Slave

(EDID)

PIO

I

2

C Slave

(SCDC)

EDID RAM

RX Core

RX

Oversampler

DCFIFO

RX Core Top

IOPLL

Transceiver PHY

Reset Controller

RX Native PHY

RX Reconfiguration

Management

IOPLL

Reconfiguration

Transceiver

Arbiter

CPU Sub-System

RX-TX Link

I

2

C

Master

PIO

TX Core

TX

Oversampler

Clock Enable

Generator

DCFIFO

TX Core Top

TX PLL

Transceiver PHY

Reset Controller

TX Native PHY

IOPLL

Reconfiguration

IOPLL

RX Audio

RX Video

RX Auxiliary

RX Sideband

TX Audio

TX Video

TX Auxiliary

TX Sideband

RX Top TX Top

Top

Parallel Data

Serial Data

Avalon-MM

Control and Status

0

To use RX or TX only components, remove the irrelevant blocks from the design

User Requirement

Preserve Remove Add

HDMI RX Only RX Top • TX Top

• RX-TX Link

• CPU Sub-System

• Transceiver Arbiter

—

HDMI TX Only TX Top, CPU Sub-System • RX Top

• RX-TX Link

• Transceiver Arbiter

Video Pattern Generator

(custom module or

generated from the VIP

Suite IP core)

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

12

Loading...

Loading...