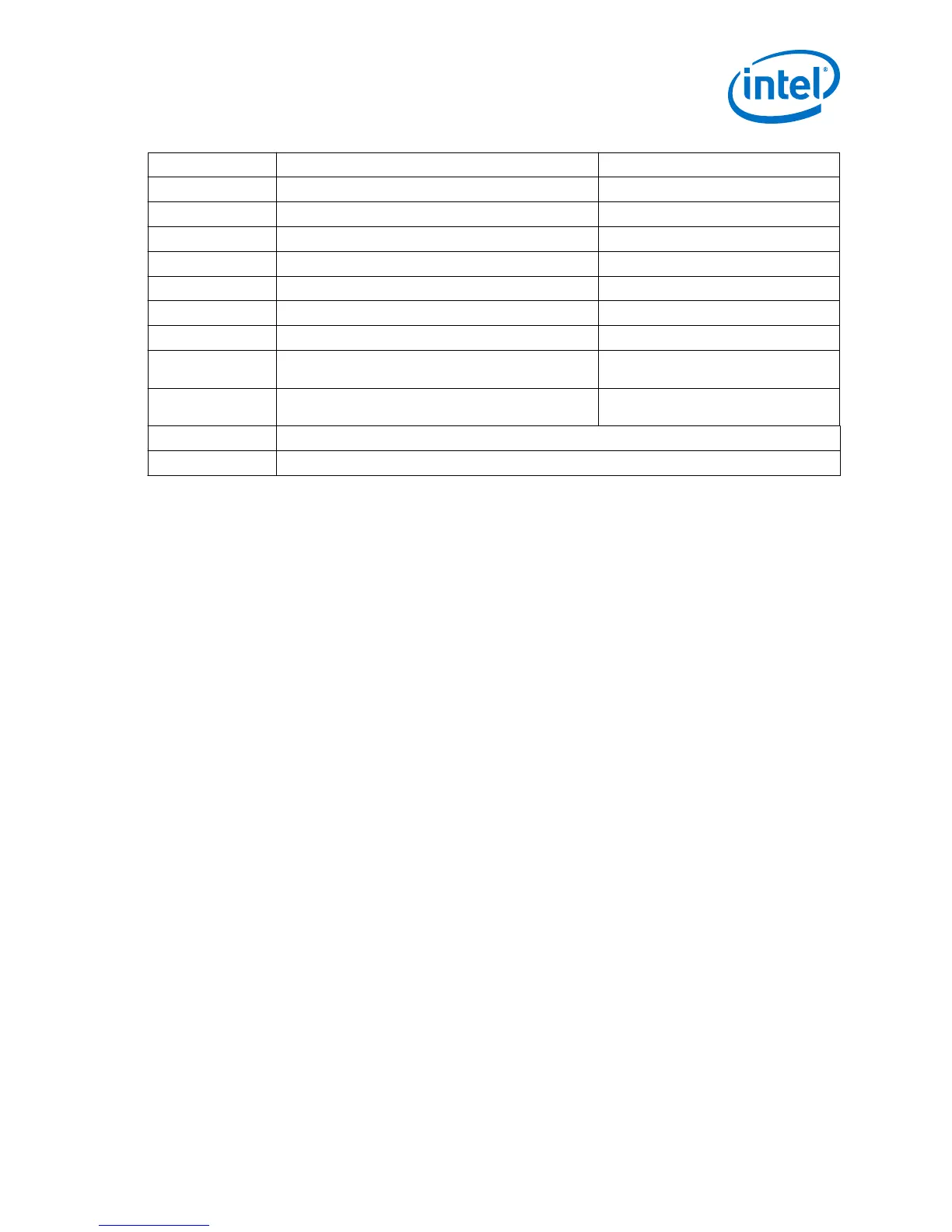

Bit-Field Definition Static Metadata Type 1

143:136 Data Byte 18: Static_Metadata_Descriptor white_point_y, MSB

151:144 Data Byte 19: Static_Metadata_Descriptor max_display_mastering_luminance, LSB

159:152 Data Byte 20: Static_Metadata_Descriptor max_display_mastering_luminance, MSB

167:160 Data Byte 21: Static_Metadata_Descriptor min_display_mastering_luminance, LSB

175:168 Data Byte 22: Static_Metadata_Descriptor min_display_mastering_luminance, MSB

183:176 Data Byte 23: Static_Metadata_Descriptor Maximum Content Light Level, LSB

191:184 Data Byte 24: Static_Metadata_Descriptor Maximum Content Light Level, MSB

199:192 Data Byte 25: Static_Metadata_Descriptor Maximum Frame-average Light Level,

LSB

207:200 Data Byte 26: Static_Metadata_Descriptor Maximum Frame-average Light Level,

MSB

215:208 Reserved

223:216 Reserved

Disabling HDR Insertion and Filtering

Disabling HDR insertion and filter enables you to verify the retransmission of HDR

content already available in the source auxiliary stream without any modification in

the RX-TX Retransmit design example.

To disable HDR Infoframe insertion and filtering:

1.

Set block_ext_hdr_infoframe to 1’b0 in the rxtx_link.v file to prevent

the filtering of the HDR Infoframe from the Auxiliary stream.

2.

Set multiplexer_in0_valid of the avalon_st_multiplexer instance in the

altera_hdmi_aux_hdr.v file to 1'b0 to prevent the Auxiliary Packet Generator

from forming and inserting additional HDR Infoframe into the TX Auxiliary stream.

2.4 Clocking Scheme

The clocking scheme illustrates the clock domains in the Intel FPGA HDMI IP core

design example.

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

23

Loading...

Loading...