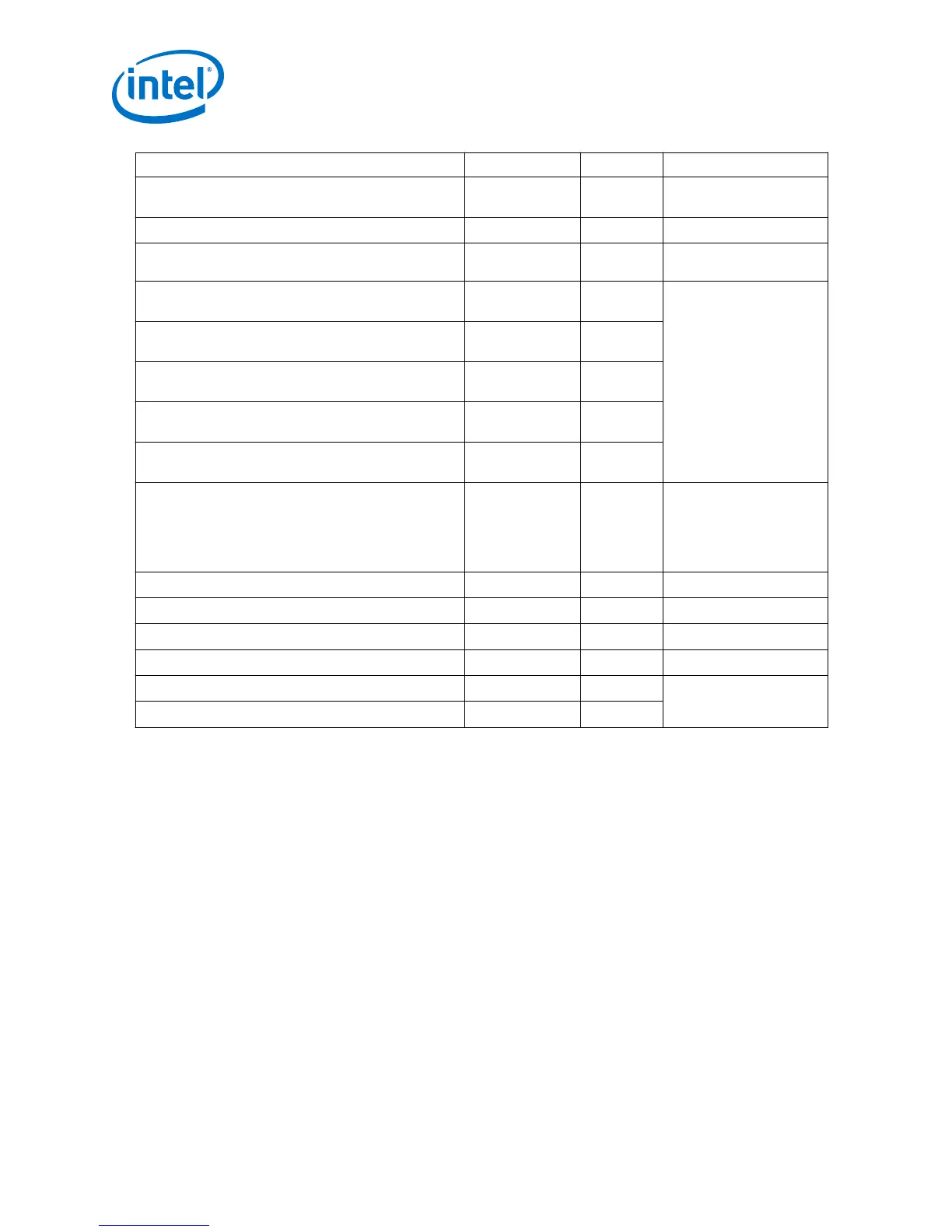

Signal Direction Width Description

tx_pma_cal_busy_pio_external_connection_exp

ort

Input 1 TX PMA Recalibration Busy

tx_pma_ch_export

Output 2 TX PMA Channels

tx_rcfg_en_pio_external_connection_export

TX PMA Reconfiguration

Enable

tx_iopll_rcfg_mgmt_translator_avalon_anti_s

lave_writedata

Output 32 TX IOPLL Reconfiguration

Avalon-MM interfaces

tx_iopll_rcfg_mgmt_translator_avalon_anti_s

lave_address

Output 9

tx_iopll_rcfg_mgmt_translator_avalon_anti_s

lave_write

Output 1

tx_iopll_rcfg_mgmt_translator_avalon_anti_s

lave_read

Output 1

tx_iopll_rcfg_mgmt_translator_avalon_anti_s

lave_readdata

Input 32

tx_os_pio_external_connection_export

Output 2 Oversampling factor:

• 0: No oversampling

• 1: 3× oversampling

• 2: 4× oversampling

• 3: 5× oversampling

tx_rst_pll_pio_external_connection_export

Output 1 Reset to IOPLL and TX PLL

tx_rst_xcvr_pio_external_connection_export

Output 1 Reset to TX Native PHY

wd_timer_resetrequest_reset

Output 1 Watchdog timer reset

color_depth_pio_external_connection_export

Input 2 Color depth

tx_hpd_ack_pio_external_connection_export

Output 1 For TX hotplug detect

handshaking

tx_hpd_req_pio_external_connection_export

Input 1

2.6 Design RTL Parameters

Use the HDMI TX and RX Top RTL parameters to customize the design example.

Most of the design parameters are available in the Intel FPGA HDMI Design Example

parameter editor. You can still change the design example settings you made in the

parameter editor through the RTL parameters.

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

36

Loading...

Loading...