Clock Signal Name in Design Description

• AVMM interfaces for reconfiguration

The frequency range requirement is between 100–125

MHz.

• PHY reset controller for transceiver reset sequence

The frequency range requirement is between 1–500

MHz.

• IOPLL Reconfiguration

Maximum clock frequency is 100 MHz.

• RX Reconfiguration for management

• CPU

• I

2

C Master

I

2

C Clock

i2c_clk

A 50 MHz clock input that clocks I

2

C slave, SCDC registers

in the HDMI RX core, and EDID RAM.

Related Links

• Using Transceiver RX Pin as CDR Reference Clock

• Using Transceiver RX Pin as TX PLL Reference Clock

2.5 Interface Signals

The tables list the signals for the Intel FPGA HDMI IP core design example.

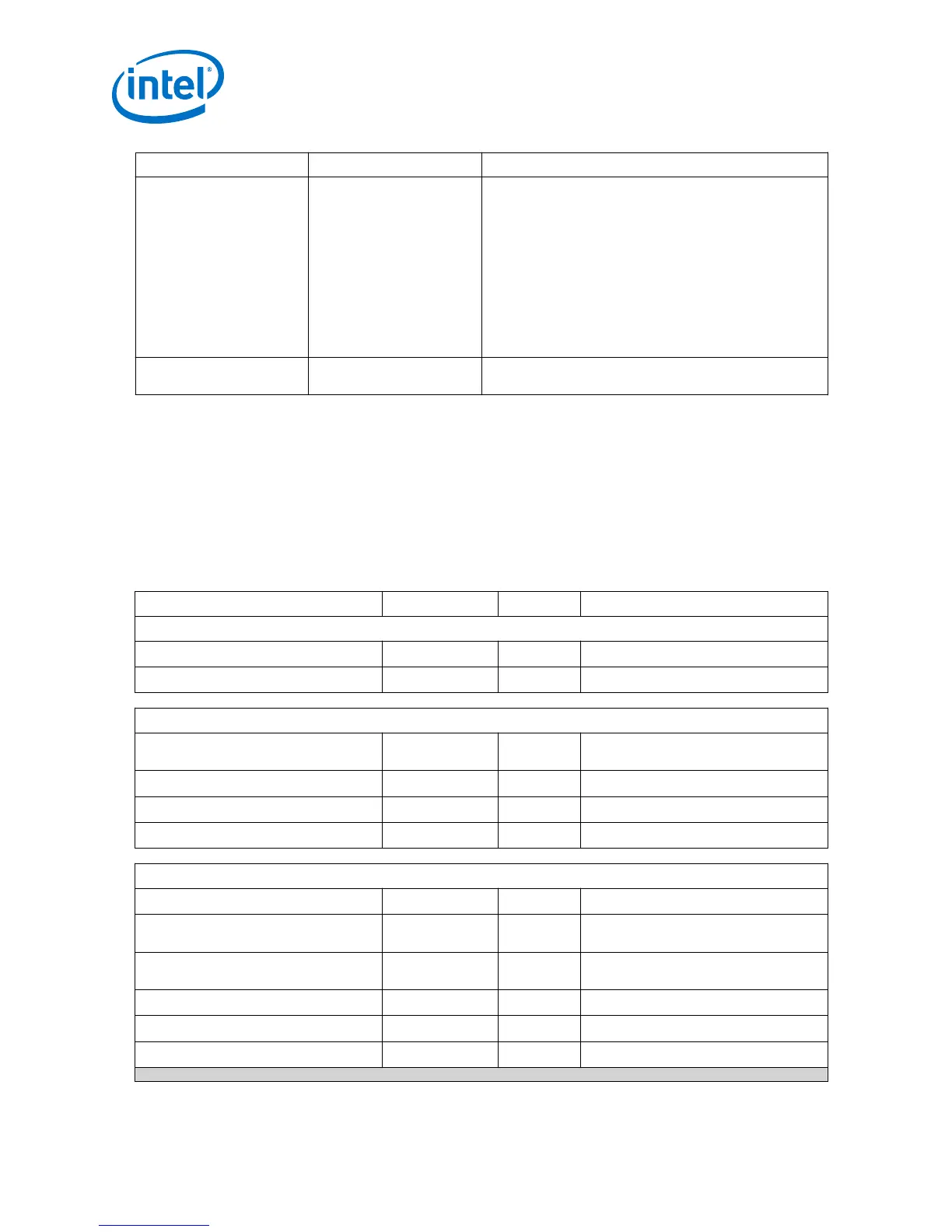

Table 15. Top-Level Signals

Signal Direction Width Description

On-board Oscillator Signal

clk_fpga_b3_p

Input 1 100 MHz free running clock

clk_50

Input 1 50 MHz free running clock

User Push Buttons and LEDs

user_pb

Input 1 Push button to control the Intel FPGA

HDMI design functionality

cpu_resetn

Input 1 Global reset

user_led_g

Output 8 Green LED display

user_led_r

Output 8 Red LED display

HDMI FMC Daughter Card Pins on FMC Port B

fmcb_gbtclk_m2c_p_0

Input 1 HDMI RX TMDS clock

fmcb_dp_m2c_p

Input 3 HDMI RX red, green, and blue data

channels

fmcb_dp_c2m_p

Output 4 HDMI TX clock, red, green, and blue data

channels

fmcb_la_rx_p_9

Input 1 HDMI RX +5V power detect

fmcb_la_rx_p_8

Inout 1 HDMI RX hot plug detect

fmcb_la_rx_n_8

Inout 1 HDMI RX I

2

C SDA

continued...

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

26

Loading...

Loading...