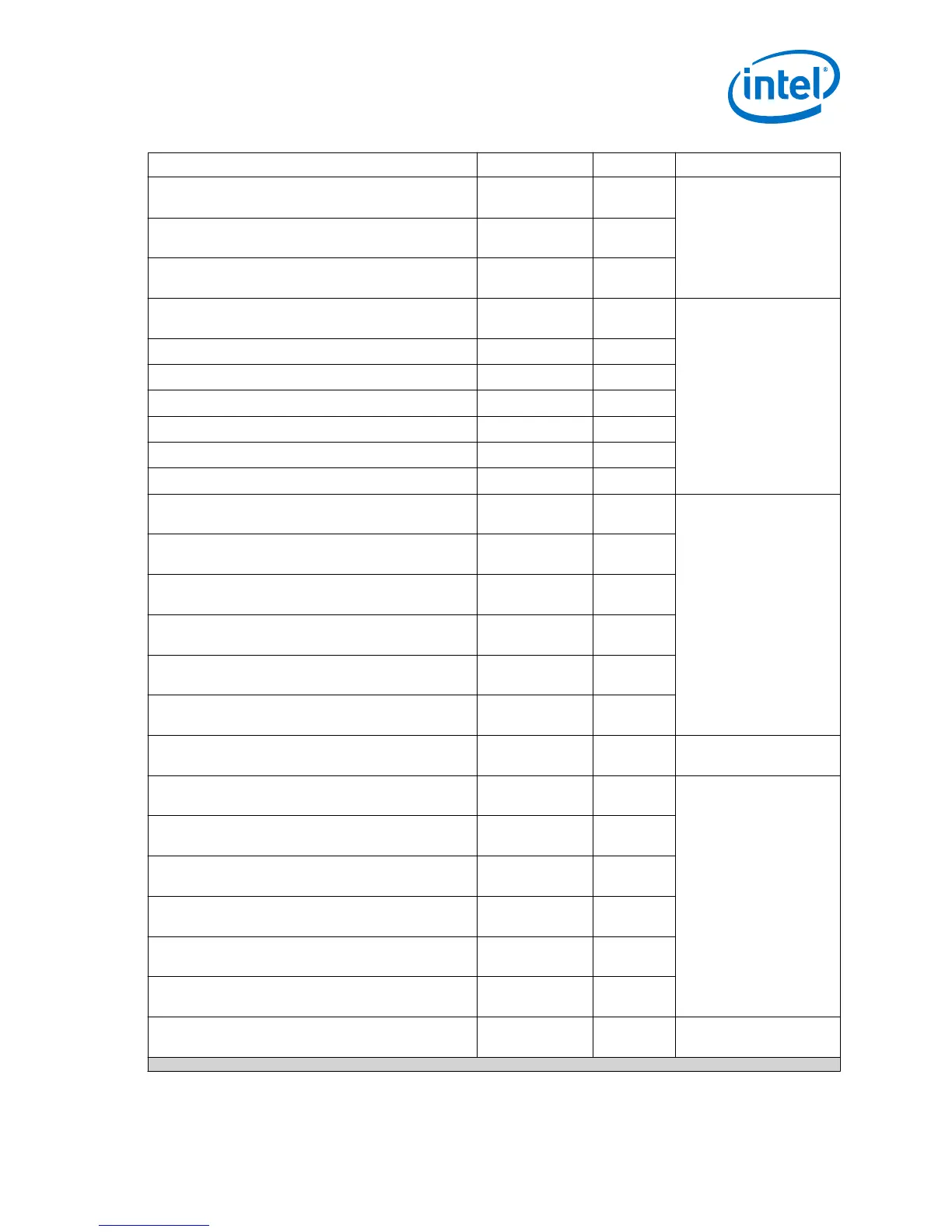

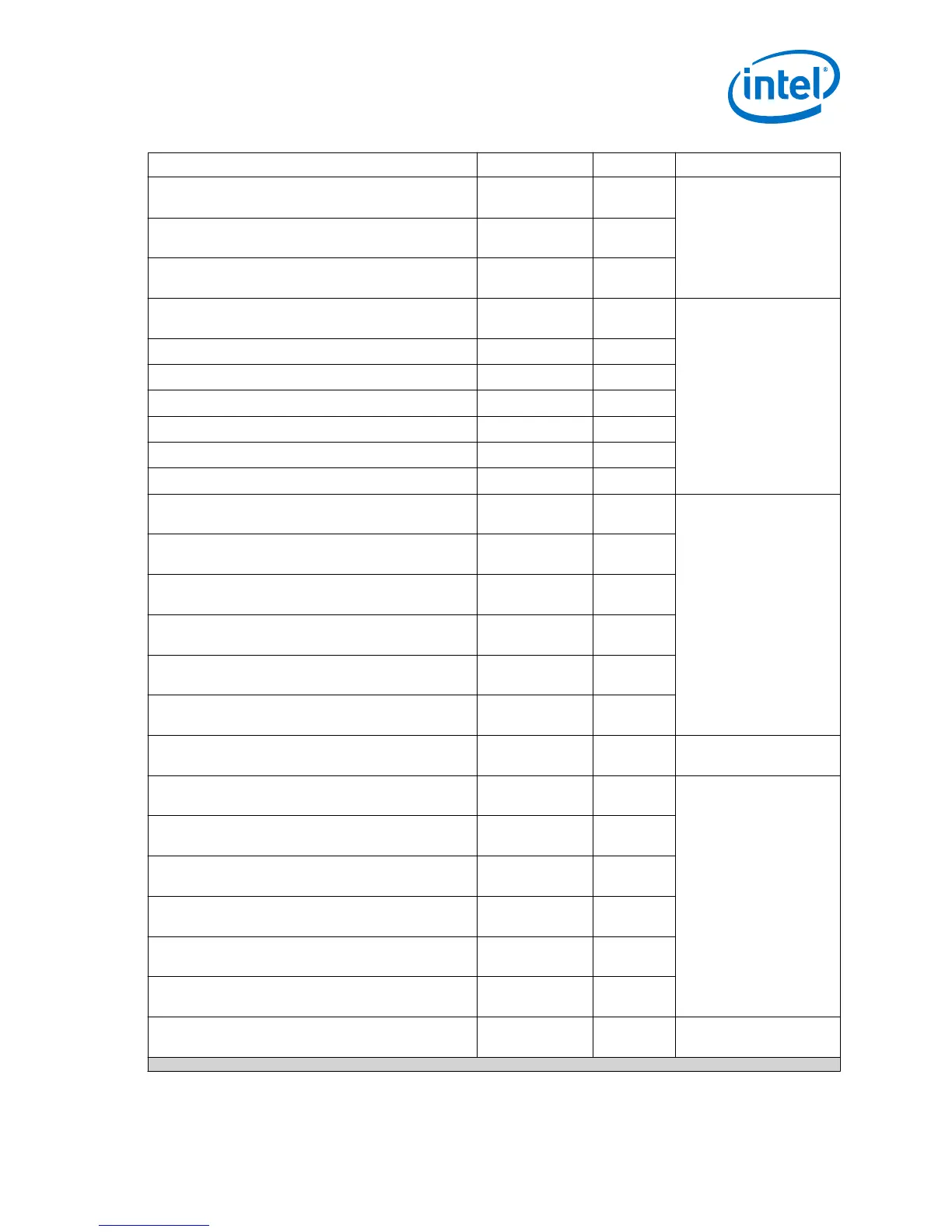

Signal Direction Width Description

oc_i2c_master_av_slave_translator_avalon_an

ti_slave_0_writedata

Output 32

oc_i2c_master_av_slave_translator_avalon_an

ti_slave_0_waitrequest

Input 1

oc_i2c_master_av_slave_translator_avalon_an

ti_slave_0_chipselect

Output 1

edid_ram_access_pio_external_connection_exp

ort

Output 1 EDID RAM access

interfaces.

Assert

edid_ram_access_pio_

external_connection_

export when you want to

write to or read from the

EDID RAM on the RX top.

Connect EDID RAM access

Avalon-MM slave in

Platform Designer to the

EDID RAM interface on the

top-level RX modules.

edid_ram_slave_translator_address

Output 8

edid_ram_slave_translator_write

Output 1

edid_ram_slave_translator_read

Output 1

edid_ram_slave_translator_readdata

Input 8

edid_ram_slave_translator_writedata

Output 8

edid_ram_slave_translator_waitrequest

Input 1

tx_pll_rcfg_mgmt_translator_avalon_anti_sla

ve_waitrequest

Input 1 TX PLL Reconfiguration

Avalon-MM interfaces

tx_pll_rcfg_mgmt_translator_avalon_anti_sla

ve_writedata

Output 32

tx_pll_rcfg_mgmt_translator_avalon_anti_sla

ve_address

Output 10

tx_pll_rcfg_mgmt_translator_avalon_anti_sla

ve_write

Output 1

tx_pll_rcfg_mgmt_translator_avalon_anti_sla

ve_read

Output 1

tx_pll_rcfg_mgmt_translator_avalon_anti_sla

ve_readdata

Input 32

tx_pll_waitrequest_pio_external_connection_

export

Input 1 TX PLL waitrequest

tx_pma_rcfg_mgmt_translator_avalon_anti_sla

ve_address

Output 12 TX PMA Reconfiguration

Avalon-MM interfaces

tx_pma_rcfg_mgmt_translator_avalon_anti_sla

ve_write

Output 1

tx_pma_rcfg_mgmt_translator_avalon_anti_sla

ve_read

Output 1

tx_pma_rcfg_mgmt_translator_avalon_anti_sla

ve_readdata

Input 32

tx_pma_rcfg_mgmt_translator_avalon_anti_sla

ve_writedata

Output 32

tx_pma_rcfg_mgmt_translator_avalon_anti_sla

ve_waitrequest

Input 1

tx_pma_waitrequest_pio_external_connection_

export

Input 1 TX PMA waitrequest

continued...

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

35

Loading...

Loading...