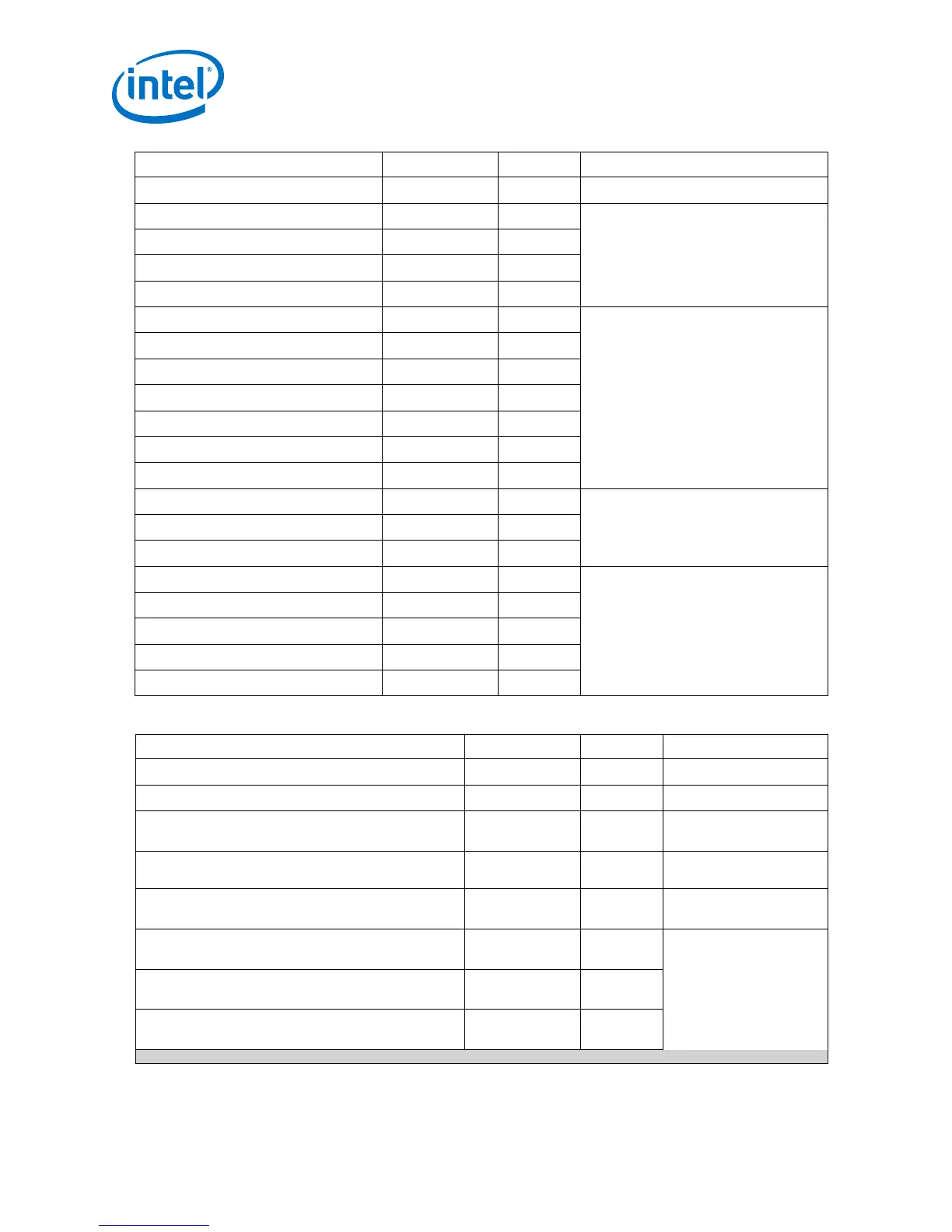

Signal Direction Width Description

rx_aux_data

Input 72

hdmi_tx_de

Output N HDMI TX video interfaces

Note: N = symbols per clock

hdmi_tx_hsync

Output N

hdmi_tx_vsync

Output N

hdmi_tx_data

Output N*48

tx_audio_format

Output 5 HDMI TX audio interfaces

tx_audio_metadata

Output 165

tx_audio_info_ai

Output 48

tx_audio_CTS

Output 20

tx_audio_N

Output 20

tx_audio_de

Output 1

tx_audio_data

Output 256

tx_gcp

Output 6 HDMI TX sideband interfaces

tx_info_avi

Output 112

tx_info_vsi

Output 61

tx_aux_eop

Output 1 HDMI TX auxiliary interfaces

tx_aux_sop

Output 1

tx_aux_valid

Output 1

tx_aux_data

Output 72

tx_aux_ready

Output 1

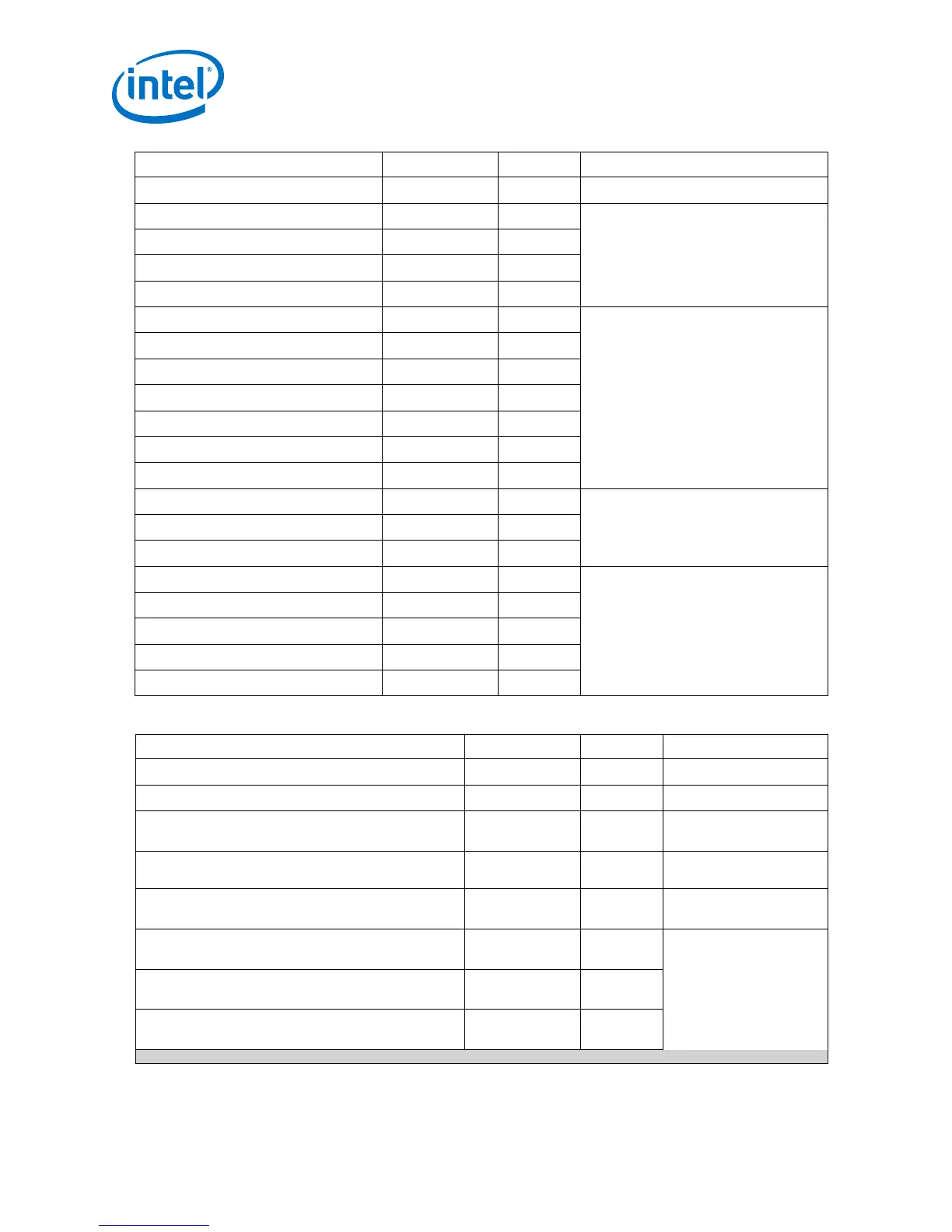

Table 20. Qsys System Signals

Signal Direction Width Description

cpu_clk

Input 1 CPU clock

cpu_clk_reset_n

Input 1 CPU reset

tmds_bit_clock_ratio_pio_external_connectio

n_export

Input 1 TMDS bit clock ratio

measure_pio_external_connection_export

Input 24 Expected TMDS clock

frequency

measure_valid_pio_external_connection_expor

t

Input 1 Indicates measure PIO is

valid

oc_i2c_master_av_slave_translator_avalon_an

ti_slave_0_address

Output 3 I

2

C Master Avalon-MM

interfaces

oc_i2c_master_av_slave_translator_avalon_an

ti_slave_0_write

Output 1

oc_i2c_master_av_slave_translator_avalon_an

ti_slave_0_readdata

32

continued...

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

34

Loading...

Loading...