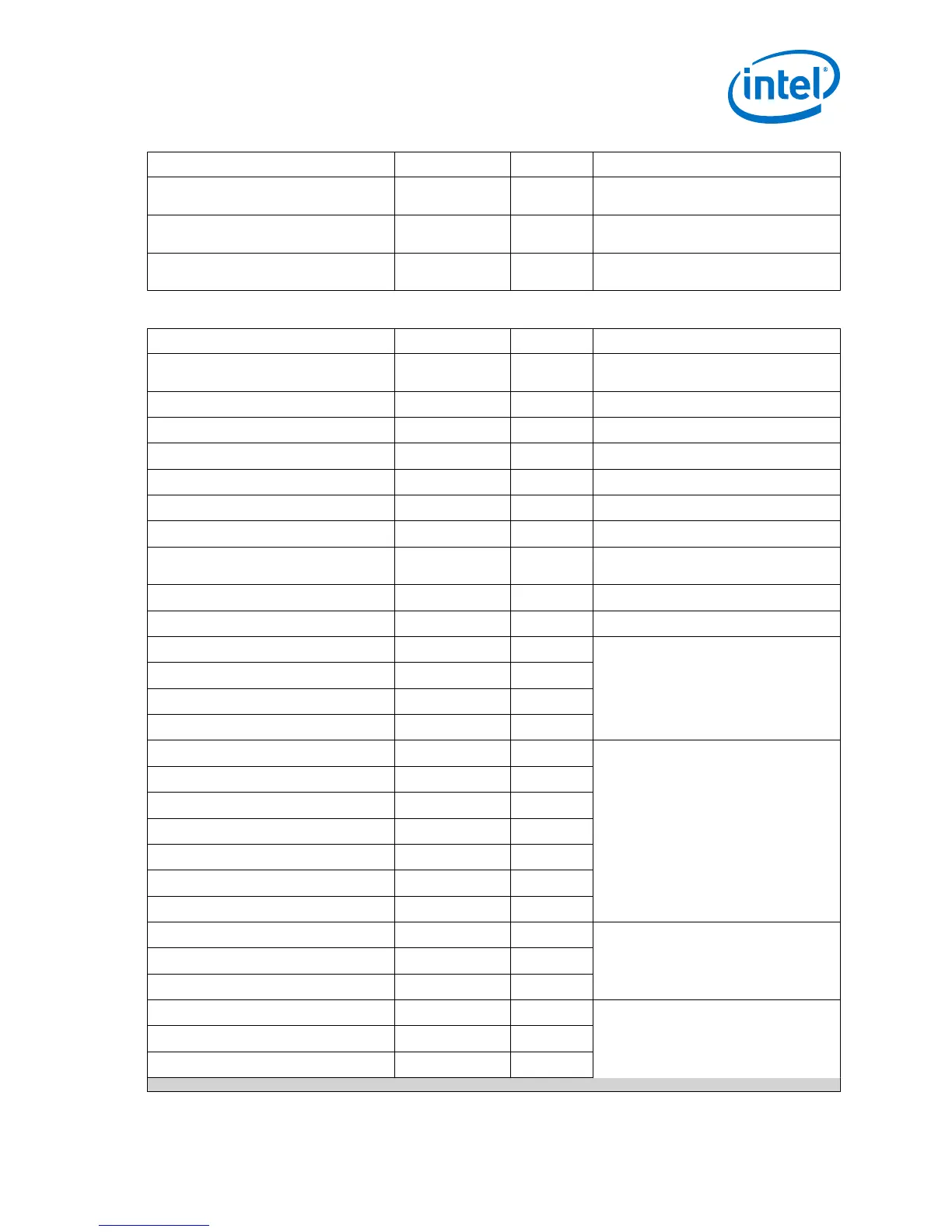

Signal Direction Width Description

tx_cal_busy

Input 1 Calibration status signal from the TX

transceiver

rx_reconfig_cal_busy

Output 1 Calibration status signal to the RX

transceiver PHY reset control

tx_reconfig_cal_busy

Output 1 Calibration status signal from the TX

transceiver PHY reset control

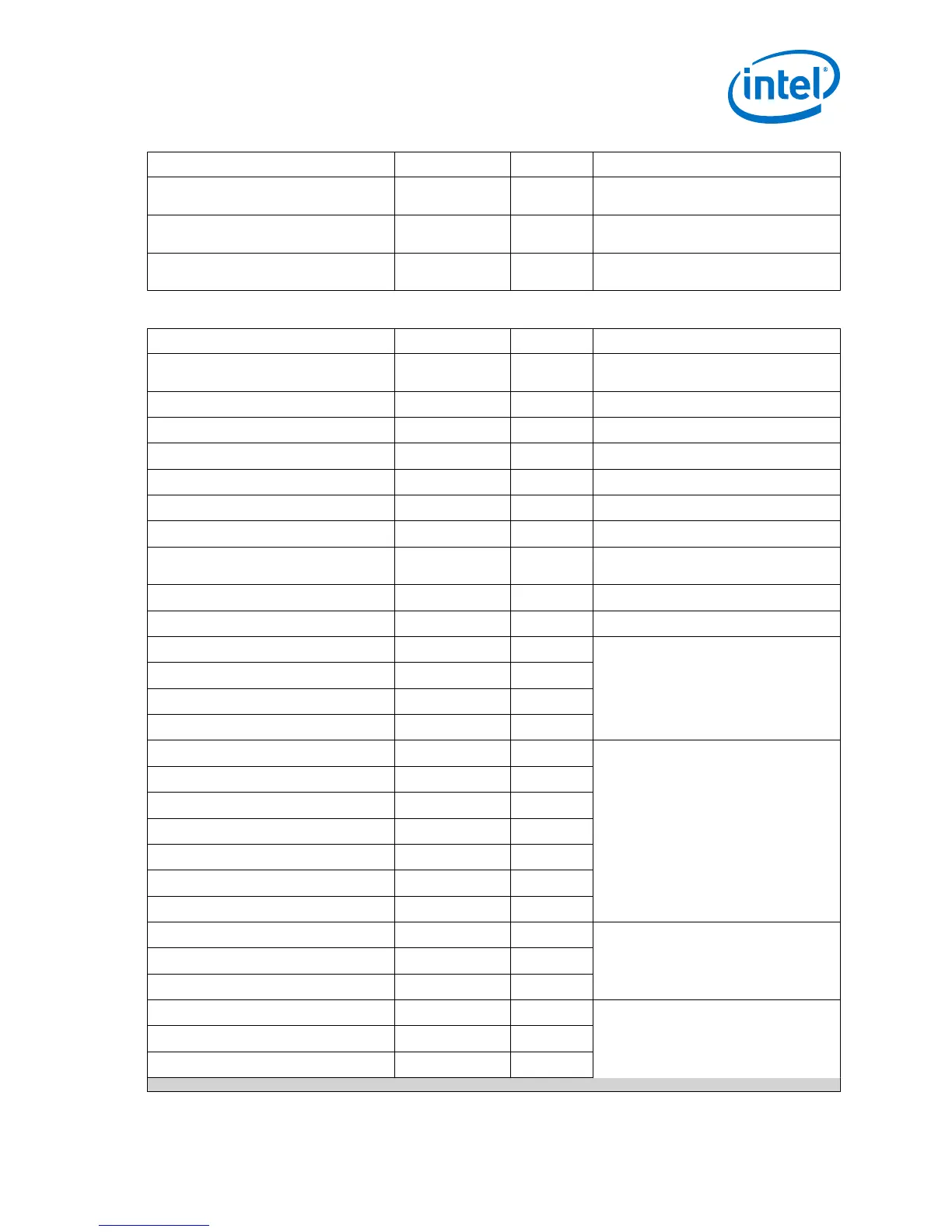

Table 19. RX-TX Link Signals

Signal Direction Width Description

reset

Input 1 Reset to the video/audio/auxiliary/

sidebands FIFO buffer.

mgmt_clk

Input 1 100 MHz clock

i2c_clk

Input 1 I

2

C clock

hdmi_tx_ls_clk

Input 1 HDMI TX link speed clock

hdmi_rx_ls_clk

Input 1 HDMI RX link speed clock

hdmi_tx_vid_clk

Input 1 HDMI TX video clock

hdmi_rx_vid_clk

Input 1 HDMI RX video clock

sys_init

Input 1 System initialization to reset the system

upon power-up

wd_reset

Input 1 Watchdog timer reset

hdmi_rx_locked

Input 3 Indicates HDMI RX locked status

hdmi_rx_de

Input N HDMI RX video interfaces

Note: N = symbols per clock

hdmi_rx_hsync

Input N

hdmi_rx_vsync

Input N

hdmi_rx_data

Input N*48

rx_audio_format

Input 5 HDMI RX audio interfaces

rx_audio_metadata

Input 165

rx_audio_info_ai

Input 48

rx_audio_CTS

Input 20

rx_audio_N

Input 20

rx_audio_de

Input 1

rx_audio_data

Input 256

rx_gcp

Input 6 HDMI RX sideband interfaces

rx_info_avi

Input 112

rx_info_vsi

Input 61

rx_aux_eop

Input 1 HDMI RX auxiliary interfaces

rx_aux_sop

Input 1

rx_aux_valid

Input 1

continued...

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

33

Loading...

Loading...