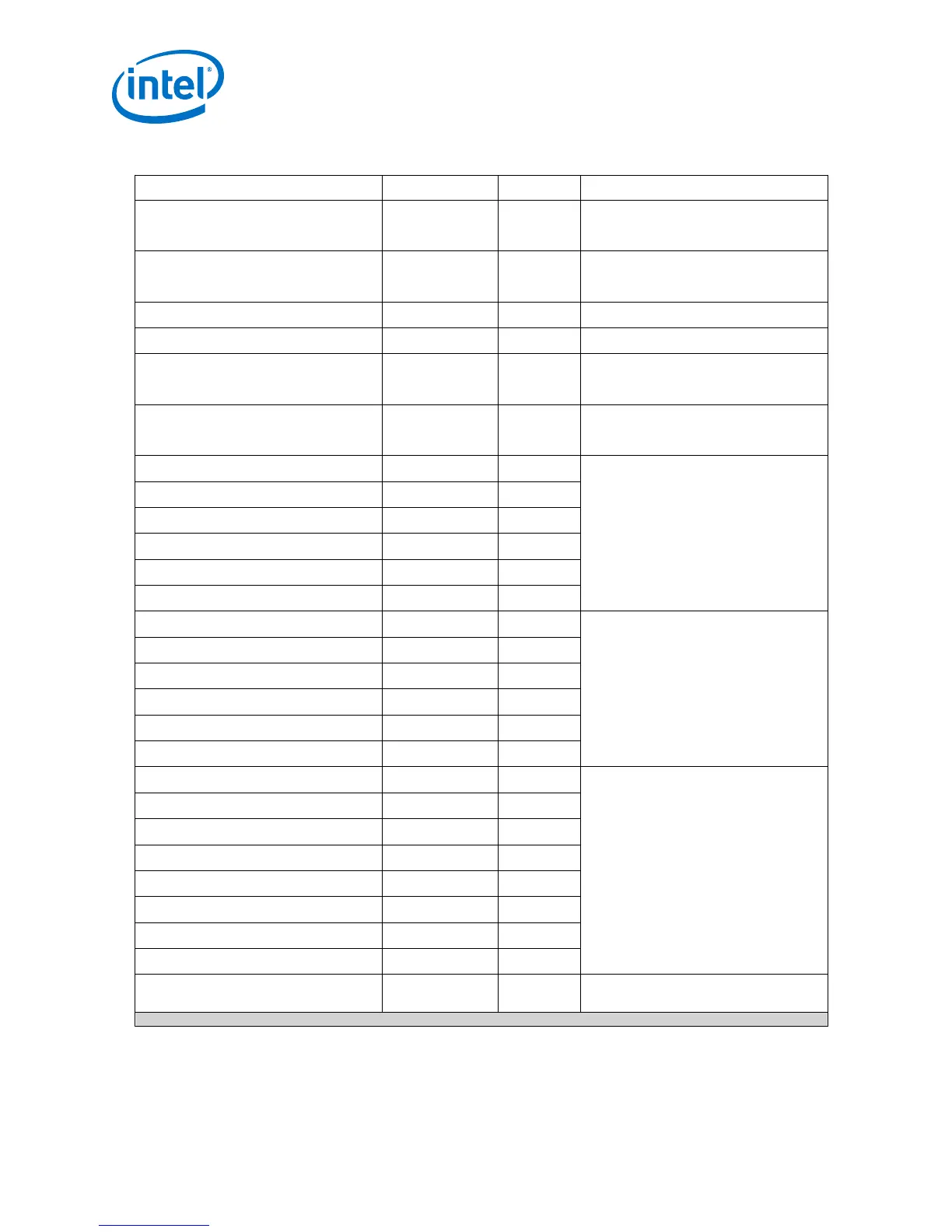

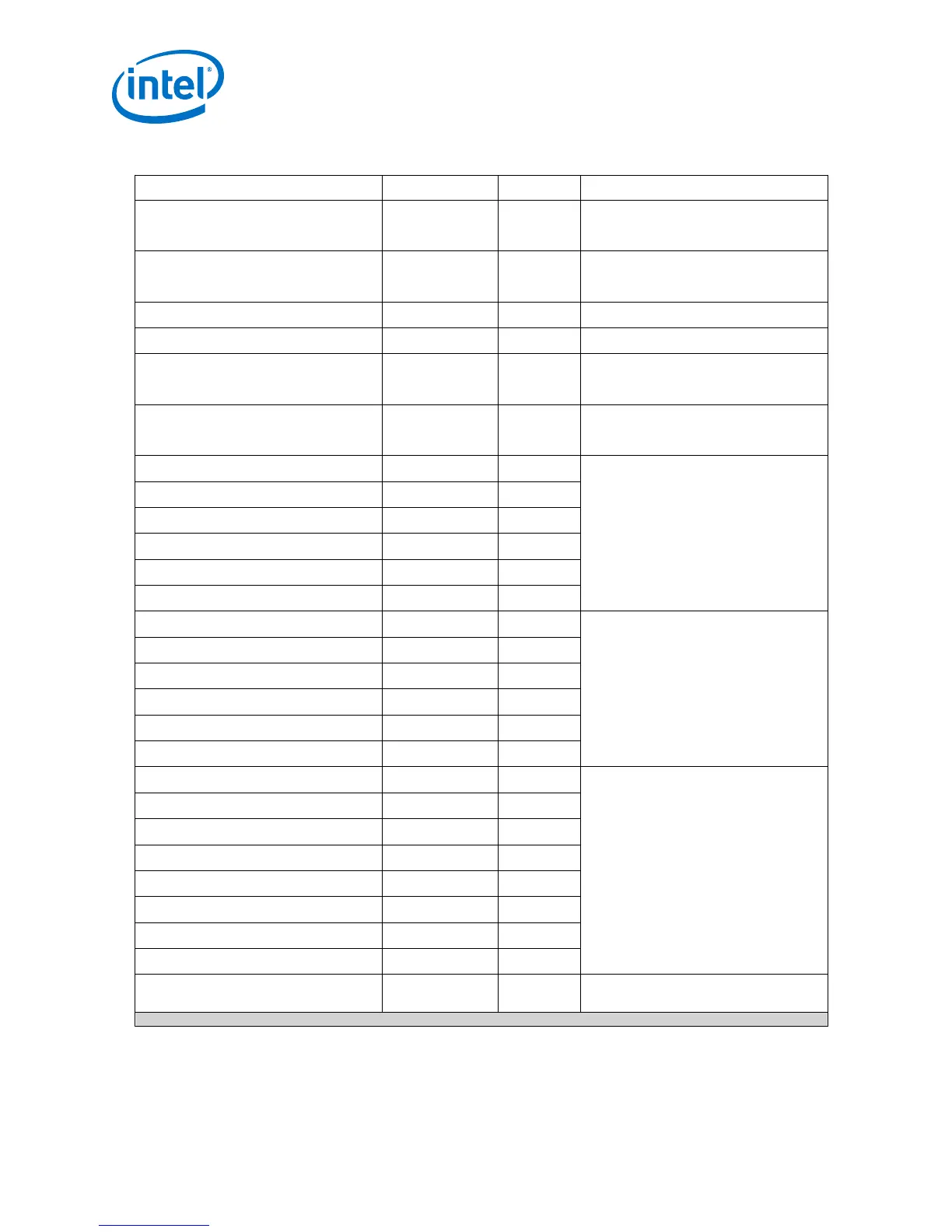

Table 18. Transceiver Arbiter Signals

Signal Direction Width Description

clk

Input 1 Reconfiguration clock. This clock must

share the same clock with the

reconfiguration management blocks.

reset

Input 1 Reset signal. This reset must share the

same reset with the reconfiguration

management blocks.

rx_rcfg_en

Input 1 RX reconfiguration enable signal

tx_rcfg_en

Input 1 TX reconfiguration enable signal

rx_rcfg_ch

Input 2 Indicates which channel to be

reconfigured on the RX core. This signal

must always remain asserted.

tx_rcfg_ch

Input 2 Indicates which channel to be

reconfigured on the TX core. This signal

must always remain asserted.

rx_reconfig_mgmt_write

Input 1 Reconfiguration Avalon-MM interfaces

from the RX reconfiguration management

rx_reconfig_mgmt_read

Input 1

rx_reconfig_mgmt_address

Input 10

rx_reconfig_mgmt_writedata

Input 32

rx_reconfig_mgmt_readdata

Output 32

rx_reconfig_mgmt_waitrequest

Output 1

tx_reconfig_mgmt_write

Input 1 Reconfiguration Avalon-MM interfaces

from the TX reconfiguration management

tx_reconfig_mgmt_read

Input 1

tx_reconfig_mgmt_address

Input 10

tx_reconfig_mgmt_writedata

Input 32

tx_reconfig_mgmt_readdata

Output 32

tx_reconfig_mgmt_waitrequest

Output 1

reconfig_write

Output 1 Reconfiguration Avalon-MM interfaces to

the transceiver

reconfig_read

Output 1

reconfig_address

Output 10

reconfig_writedata

Output 32

rx_reconfig_readdata

Input 32

rx_reconfig_waitrequest

Input 1

tx_reconfig_readdata

Input 1

tx_reconfig_waitrequest

Input 1

rx_cal_busy

Input 1 Calibration status signal from the RX

transceiver

continued...

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

32

Loading...

Loading...