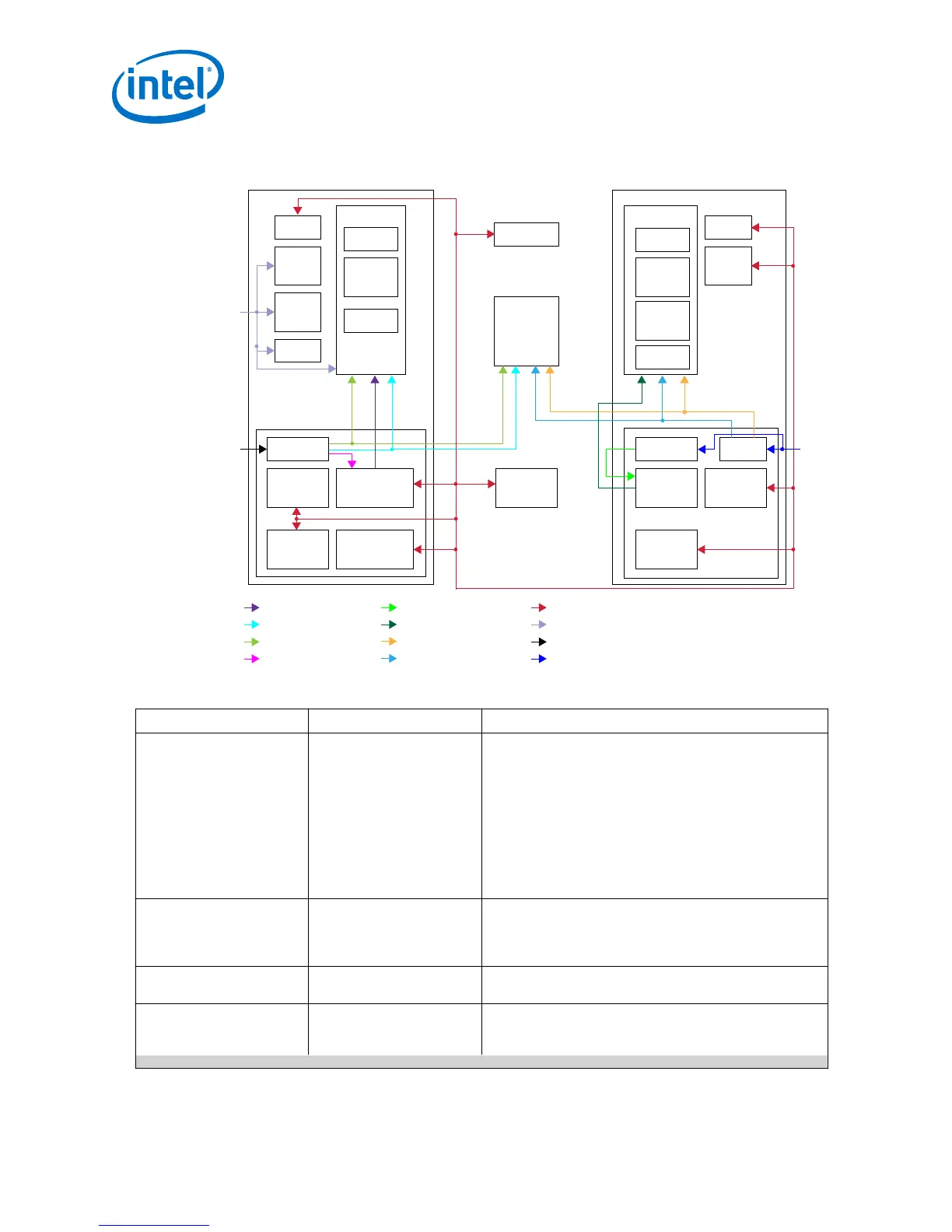

Figure 10. Intel FPGA HDMI Design Example Clocking Scheme

I

2

C Slave

(EDID)

PIO

I

2

C Slave

(EDID)

EDID RAM

RX Core

RX

Oversampler

DCFIFO

RX Core Top

IOPLL

Transceiver PHY

Reset Controller

RX Native PHY

RX Reconfiguration

Management

IOPLL

Reconfiguration

Transceiver

Arbiter

CPU Sub-System

RX-TX Link

I

2

C

Master

PIO

TX Core

TX

Oversampler

DCFIFO

TX Core Top

TX PLL

Transceiver PHY

Reset Controller

TX Native PHY

IOPLL

Reconfiguration

IOPLL

RX Top TX Top

Top

RX Transceiver Clock Out

RX Link Speed Clock

RX Video Clock

RX CDR Reference Clock

TX PLL Serial Clock Management Clock

I

2

C Clock

RX TMDS Clock

TX IOPLL/TX PLL Reference Clock

TX Transceiver Clock Out

TX Link Speed Clock

TX Video Clock

Clock Enable

Generator

Table 14. Clocking Scheme Signals

Clock Signal Name in Design Description

TX IOPLL/ TX PLL Reference

Clock

hdmi_clk_in

Reference clock to the TX IOPLL and TX PLL. The clock

frequency is the same as the expected TMDS clock

frequency from the HDMI TX TMDS clock channel.

For this Intel FPGA HDMI design example, this clock is

connected to the RX TMDS clock for demonstration purpose.

In your application, you need to supply a dedicated clock

with TMDS clock frequency from a programmable oscillator

for better jitter performance.

Note:

Do not use a transceiver RX pin as a TX PLL

reference clock. Your design will fail to fit if you

place the HDMI TX refclk on an RX pin.

TX Transceiver Clock Out

tx_clk

Clock out recovered from the transceiver, and the frequency

varies depending on the data rate and symbols per clock.

TX transceiver clock out frequency = Transceiver data rate/

(Symbol per clock*10)

TX PLL Serial Clock

tx_bonding_clocks

Serial fast clock generated by TX PLL. The clock frequency is

set based on the data rate.

TX/RX Link Speed Clock

ls_clk

Link speed clock. The link speed clock frequency depends

on the expected TMDS clock frequency, oversampling factor,

symbols per clock, and TMDS bit clock ratio.

continued...

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

24

Loading...

Loading...