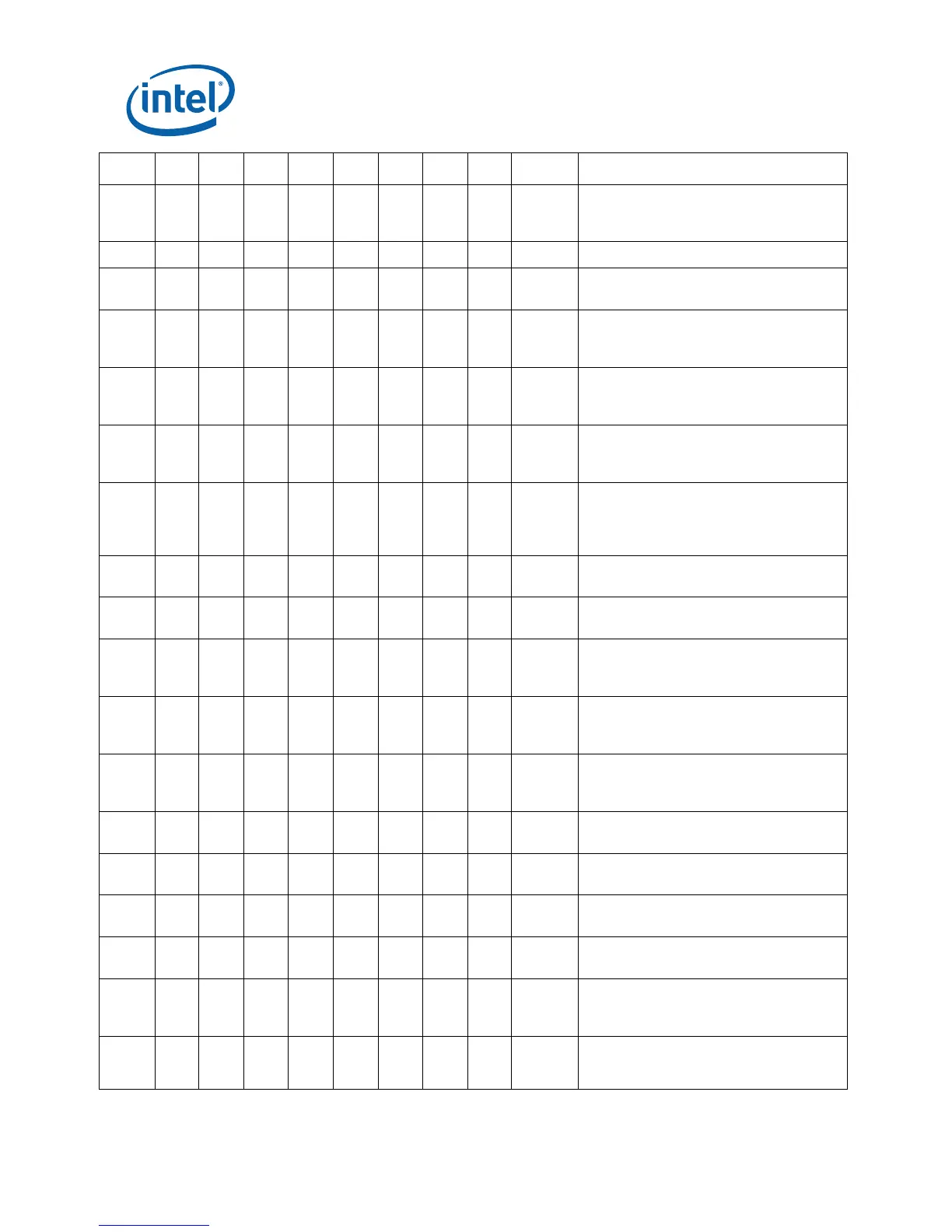

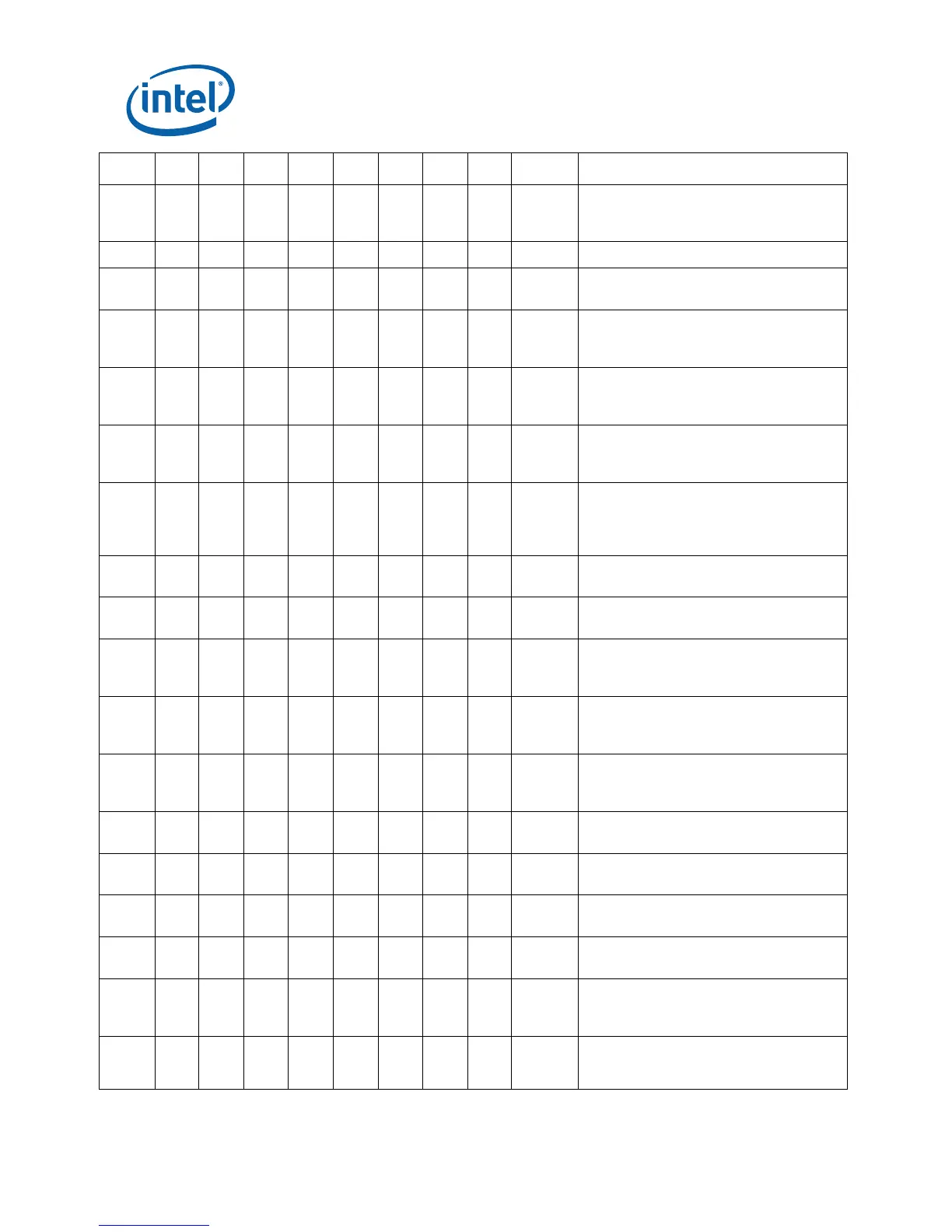

Summary Tables of Changes

14 Specification Update

No. B2 C1 D0 E0 B0 C1 D1 M0 Plan ERRATA

N3 X X X X Fixed

Uncacheable (UC) code in same line as

write back (WB) data may lead to data

corruption

N4 X X X X X X X X No Fix Transaction is not retried after BINIT#

N5 X X X X X X X X No Fix

Invalid opcode 0FFFh requires a ModRM

byte

N6 X Fixed

RFO-ECC-snoop-MCA combination can

result in two lines being corrupted in

main memory

N7 X Fixed

Overlap of MTRRs with the same

memory type results in a type of

uncacheable (UC)

N8 X X X X X X X X No Fix

FSW may not be completely restored

after page fault on FRSTOR or FLDENV

instructions

N9 X X X X X X X X No Fix

The Processor Signals Page-Fault Exception

(#PF) Instead of Alignment Check Exception

(#AC) on an Unlocked CMPXCHG8B

Instruction

N10 X Fixed

IERR# may not go active when an

internal error occurs

N11 X Fixed

All L2 cache uncorrectable errors are

logged as data writes

N12 X X X X X X X X No Fix

When in no-fill mode the memory type

of large pages are incorrectly forced to

uncacheable

N13 X X X X X X X X No Fix

Processor may hang due to speculative

page walks to non-existent system

memory

N14 X Fixed

Load operations may get stale data in

the presence of memory address

aliasing

N15 X X X X Fixed

Writing a performance counter may

result in incorrect value

N16 X X X X Fixed

IA32_MC0_STATUS register overflow

bit not set correctly

N17 X X X X Fixed

Performance counter may contain

incorrect value after being stopped

N18 X Fixed

The TAP drops the last bit during

instruction register shifting

N19 X Fixed

Data breakpoints on the high half of a

floating point line split may not be

captured

N20 X X X X Fixed

MCA error code field in

IA32_MC0_STATUS register may

become out of sync with the rest of the

Loading...

Loading...