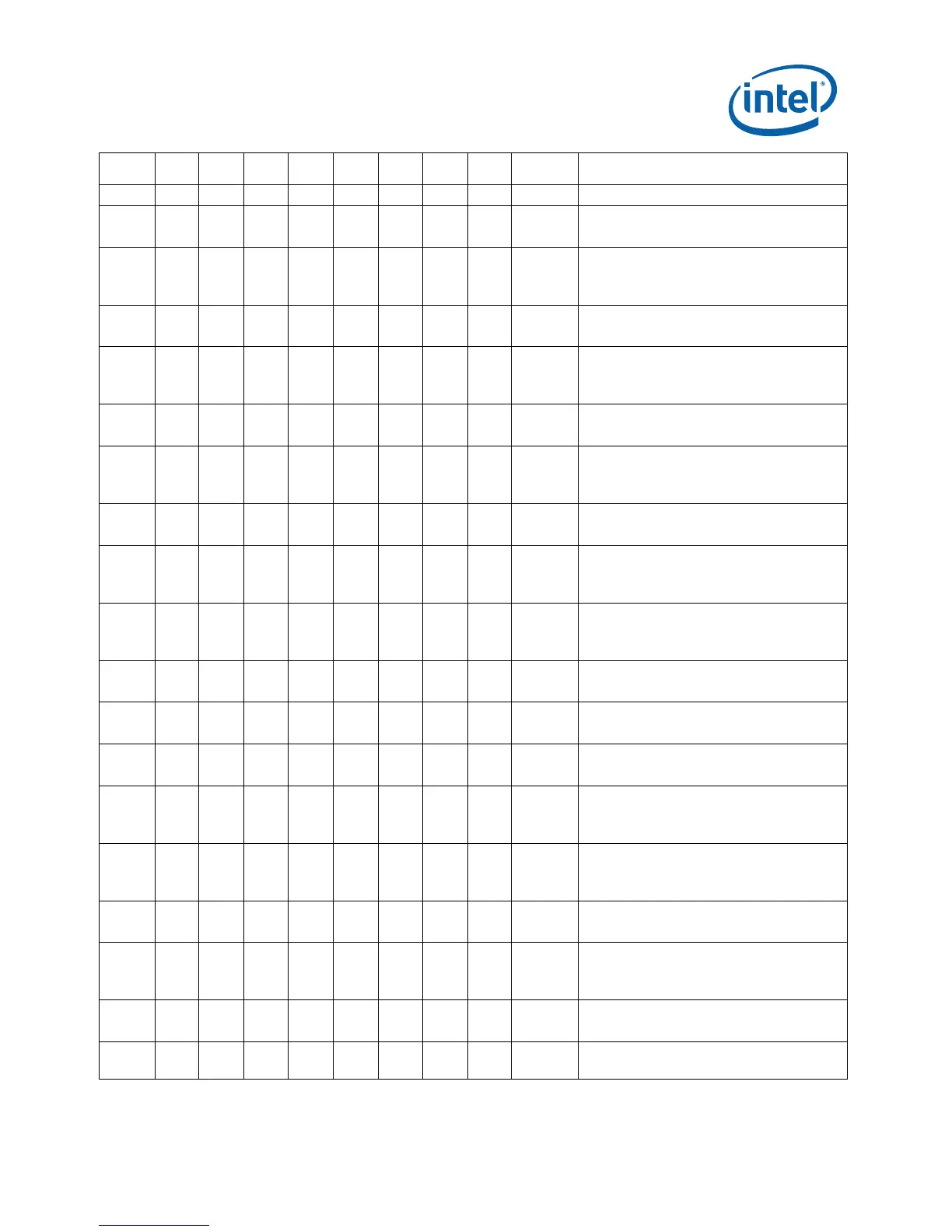

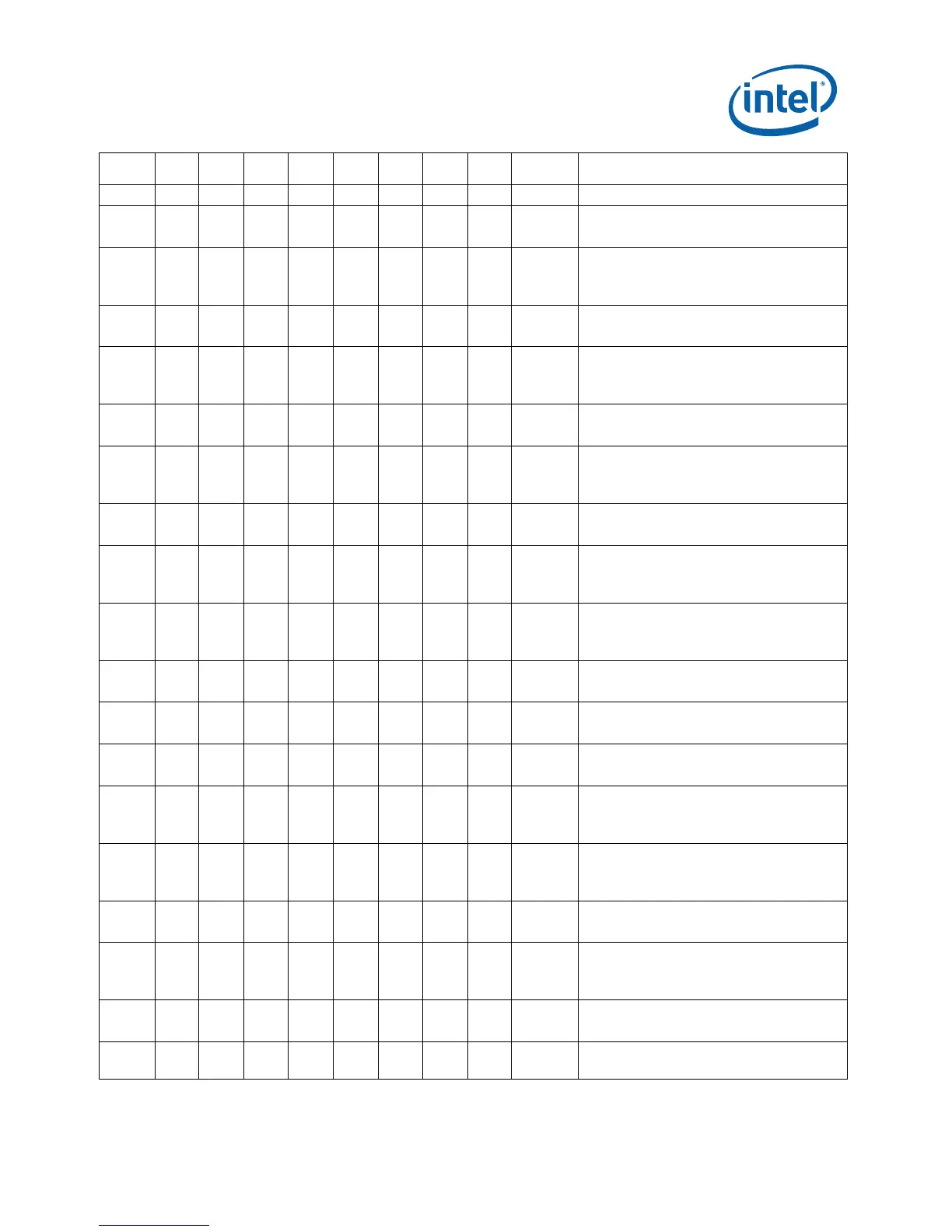

Summary Tables of Changes

Specification Update 15

No. B2 C1 D0 E0 B0 C1 D1 M0 Plan ERRATA

register

N21 X Fixed

Processor may hang on a correctable

error and snoop combination

N22 X X X X X X X X No Fix

The IA32_MC1_STATUS register may

contain incorrect information for

correctable errors

N23 X Fixed

MCA error incorrectly logged as

prefetches

N24 X Fixed

Speculative loads which hit the L2

cache and get an uncorrectable error

will log erroneous information

N25 X Fixed

Processor may fetch reset vector from

cache if A20M# is asserted during init

N26 X Fixed

A correctable error on an L2 cache

shared state line hit with go to invalid

snoop hangs processor

N27 X Fixed

System hang due to uncorrectable

error and bus lock combination

N28 X Fixed

Incorrect address for an L1 tag parity

error is logged in IA32_MC1_ADDR

register

N29 X X Fixed

REP MOV instruction with overlapping

source and destination may result in

data corruption

N30 X Fixed

Stale data in processor translation

cache may result in hang

N31 X Fixed

I/O buffers for FERR#, PROCHOT# and

THERMTRIP# are not AGTL+

N32 X Fixed

RFO and correctable error combination

may cause lost store or hang

N33 X Fixed

RFO and correctable error may

incorrectly signal the machine check

handler

N34 X Fixed

Processor may report invalid TSS fault

instead of double fault during mode C

paging

N35 X Fixed

IA32_MC0_STATUS incorrect after

illegal APIC request

N36 X X Fixed

Thermal status log bit may not be set

when the thermal control circuit is

active

N37 X X X X X X X X No Fix

Debug mechanisms may not function

as expected

N38 X X X X X X X X No Fix

Machine check architecture error

reporting and recovery may not work

Loading...

Loading...