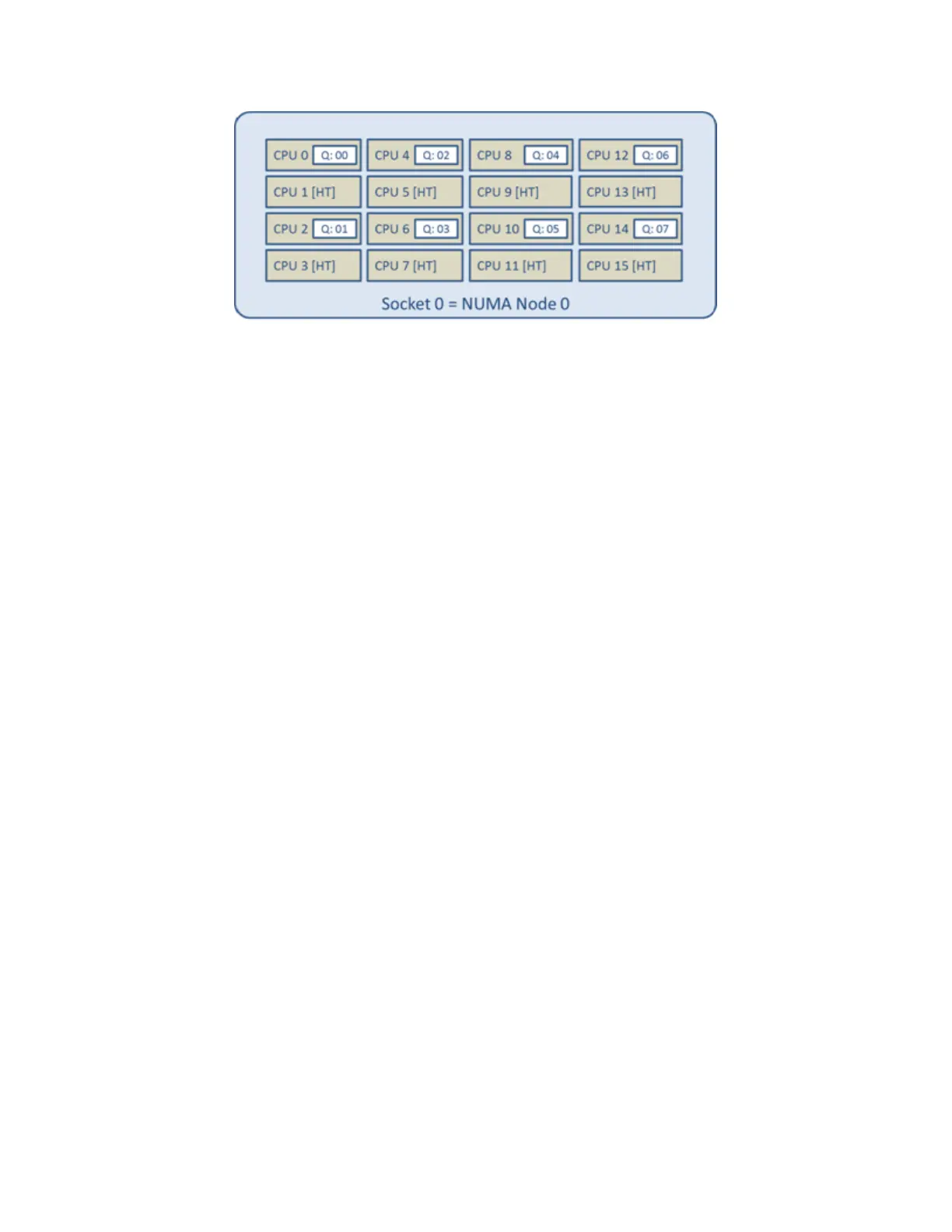

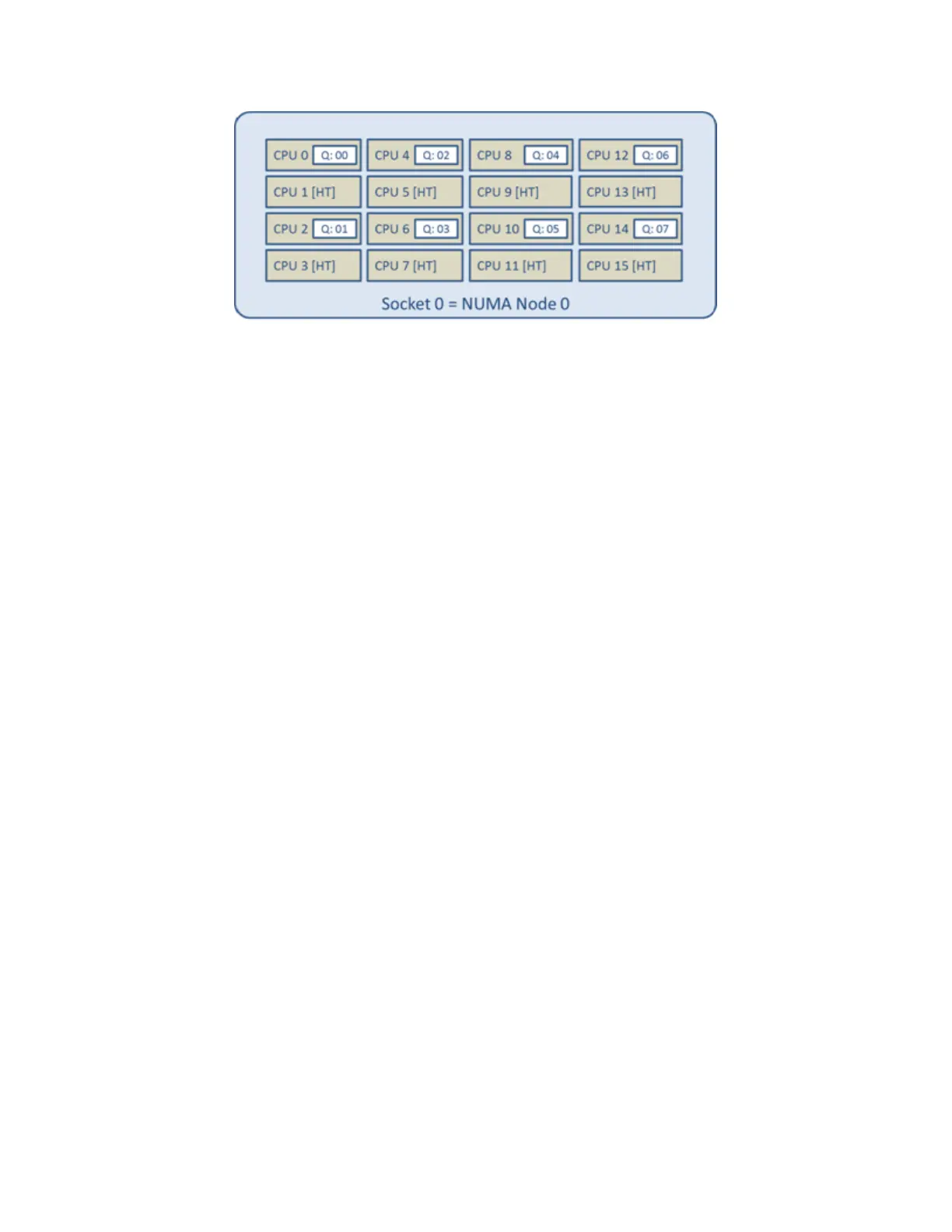

Socket Queue to CPU Allocation

Using the performance tuning options, you can direct association of the FCoE queues for the second port to a

different non-competing set of CPU cores. The following settings would direct SW to use CPUs on the other

processor socket:

l FCoE NUMA Node Count = 1: Assign queues to cores from a single NUMA node (or processor

socket)

l FCoE Starting NUMA Node = 1:Use CPU cores from the second NUMA node (or processor socket)

in the system

l FCoE Starting Core Offset = 0:SW will start at the first CPU core of the NUMA node (or processor

socket)

The following settings would direct SW to use a different set of CPUs on the same processor socket (this

assumes a processor that supports 16 non-HT cores):

l FCoE NUMA Node Count = 1

l FCoE Starting NUMA Node = 0

l FCoE Starting Core Offset = 8

Example 2:

You would like to experiment with having one or more ports with queues allocated across multiple NUMA

nodes. In this case, for each NIC port you would set FCoE NUMA Node Count to that number of NUMA

nodes. By default the queues will be allocated evenly from each NUMA node:

l FCoE NUMA Node Count = 2

l FCoE Starting NUMA Node = 0

l FCoE Starting Core Offset = 0

Example 3:

You learn that the FCoE Port NUMA Node setting is 2 for a given NIC port.This is a read-only indication from

SW that the optimal nearest NUMA node to the PCI device is the third logical NUMA node in the system. Yet

by default SW has allocated that port’s queues to NUMA node 0. The following settings would direct SW to

use CPUs on the optimal processor socket:

l FCoE NUMA Node Count = 1

l FCoE Starting NUMA Node = 2

l FCoE Starting Core Offset = 0

This example highlights the fact that platform architectures can vary in the number of PCI buses and where

they are attached. To help understand this, the figures below show two simplified platform architectures. The

first is the older common FSB style architecture in which multiple CPUs share access to a single MCH and/or

Loading...

Loading...