Notes:

1. A1 is the least significant address bit.

2. A23 is valid for 128-Mbit densities and above; otherwise, it is a no connect (NC).

3. A24 is valid for 256-Mbit densities; otherwise, it is a no connect (NC).

4. Synchronous burst read operation is currently not supported for the TSOP package. The synchronous

read input signals (i.e. ADV# and CLK) should be tied off to support asynchronous reads.

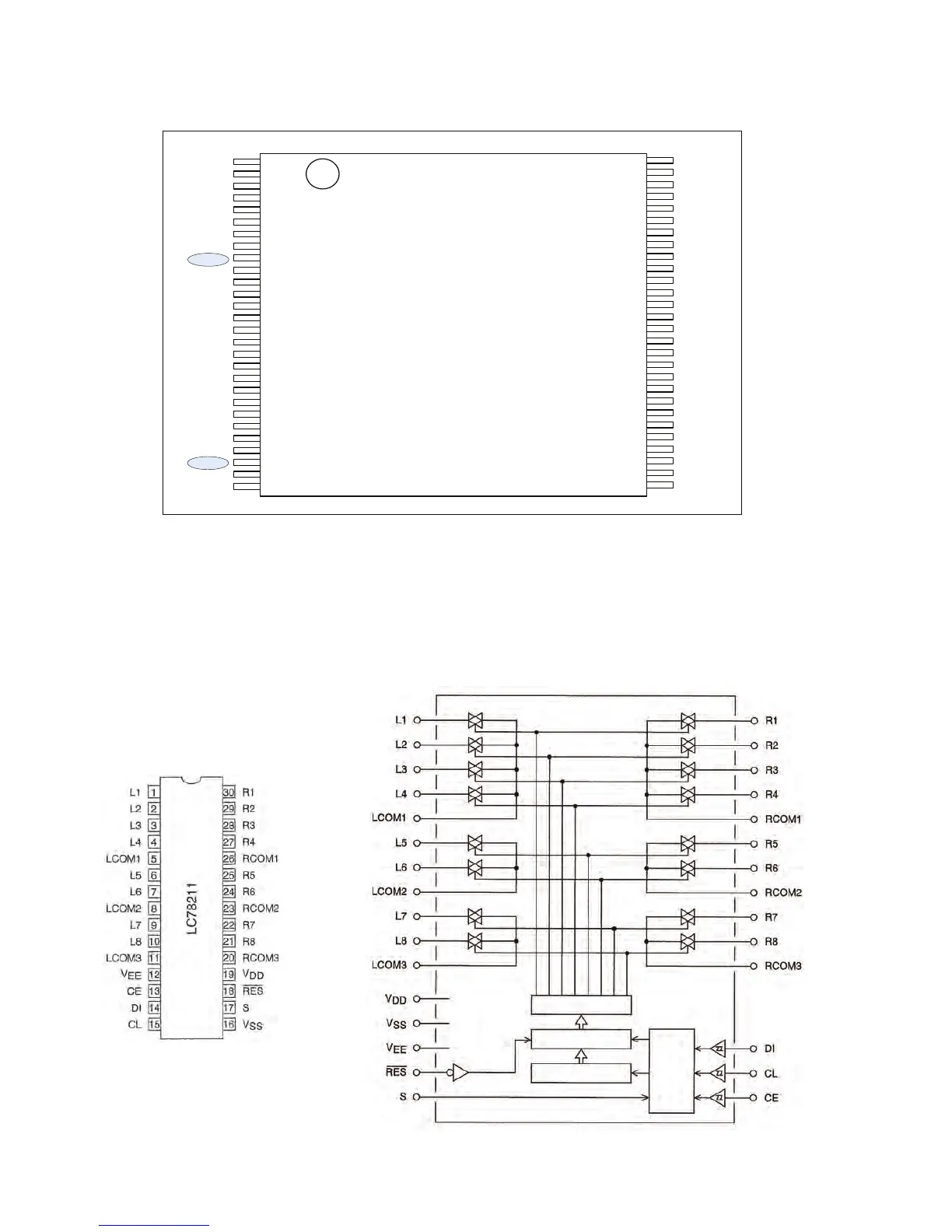

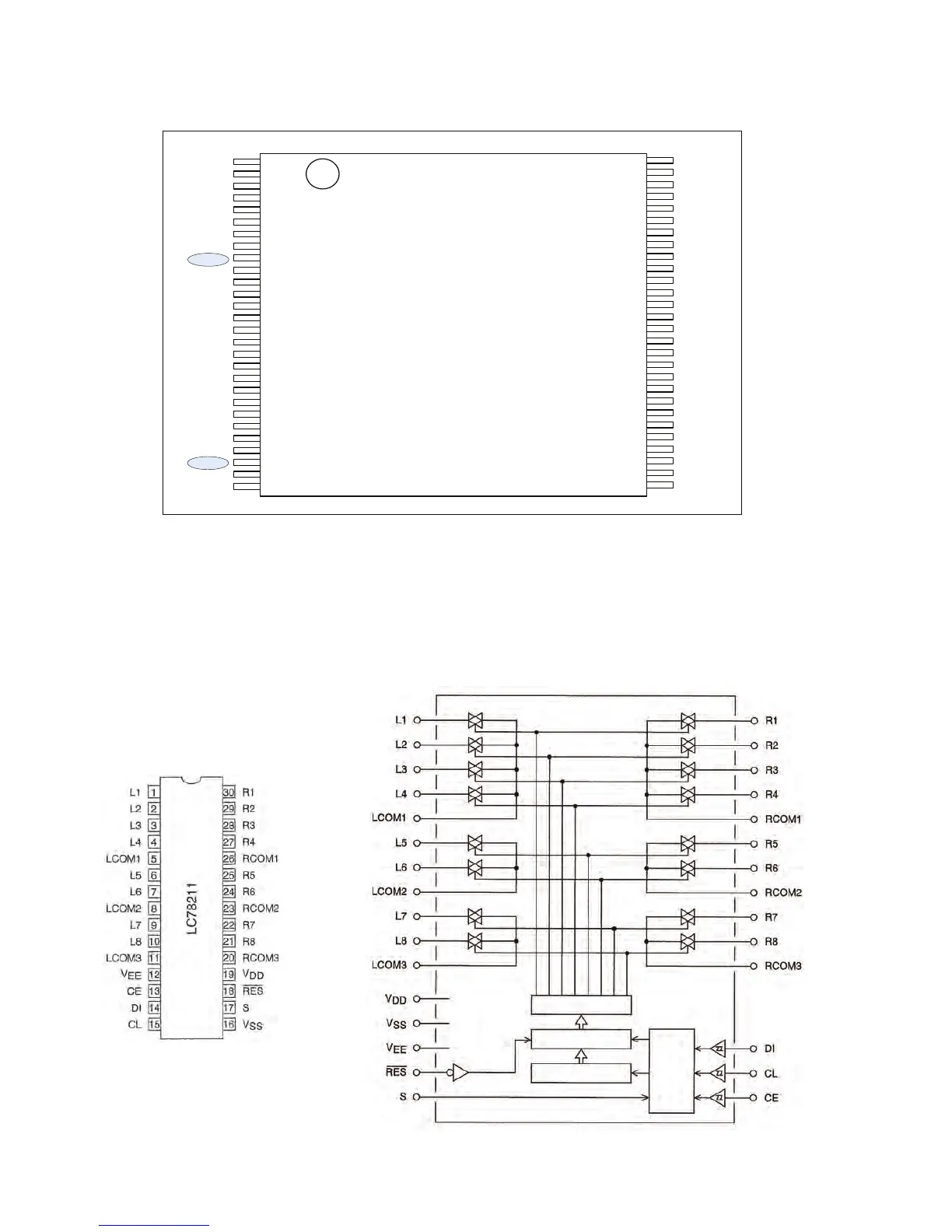

Intel StrataFlash®

Embedded Memory (P30)

56-Lead TSOP Pinout

14 mm x 20 mm

Top View

1

3

4

2

5

7

8

6

9

11

12

10

13

15

16

14

17

19

20

18

21

23

24

22

25

27

28

26

56

54

53

55

52

50

49

51

48

46

45

47

44

42

41

43

40

38

37

39

36

34

33

35

32

30

29

31

A14

A13

A12

A10

A9

A11

A23

A21

VSS

A22

VCC

WP#

A20

WE#

A19

A8

A7

A18

A6

A4

A3

A5

A2

RFU

VSS

A24

WAIT

DQ15

DQ7

A17

DQ14

DQ13

DQ5

DQ6

DQ12

ADV#

CLK

DQ4

RST#

A16

DQ3

VPP

DQ10

VCC

Loading...

Loading...