5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

(Default)

CFG4

1: DISABLED;

NO PHYSICAL DISPLAY PORT ATTACHED

TO EMBEDDED DISPLAY PORT

0:ENABLED; AN EXTERNAL DISPLAY PORT DEVICE

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

DISPLAY PORT PRESENCE STRAP

NOTE:

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

0 : ENABLED SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

1 : DISABLED

3G

FAN

WLAN

CPU

OPI_RCOMP

CFG_RCOMP

TD_IREF

CFG4

CFG3

CFG4

CFG3

GND

GND

GND

GND

GND

GND

GNDGNDGND

GND

GND

GND

VCCIN9,31

Title

Size Document Number Rev

Date: Sheet

of

1.0

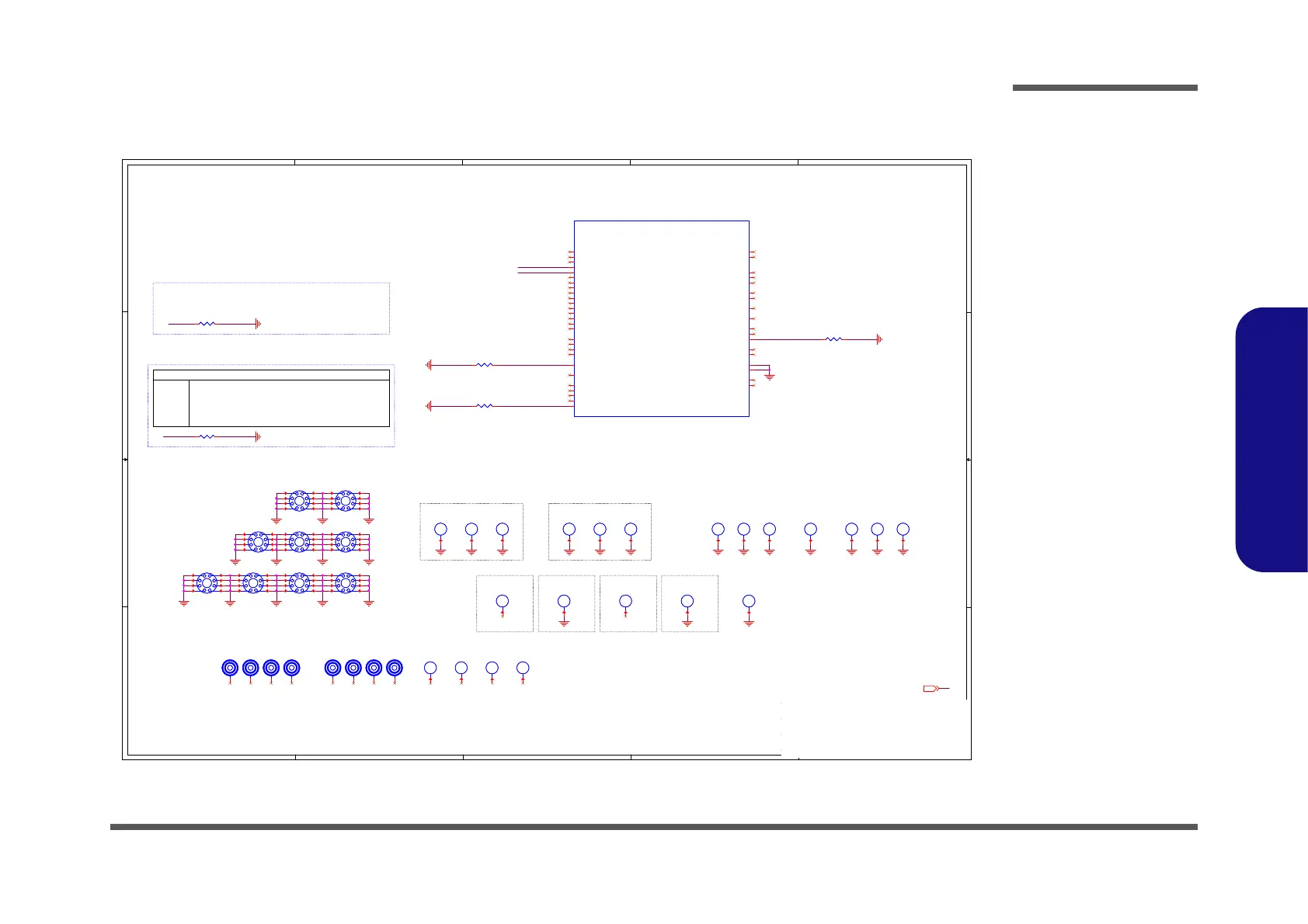

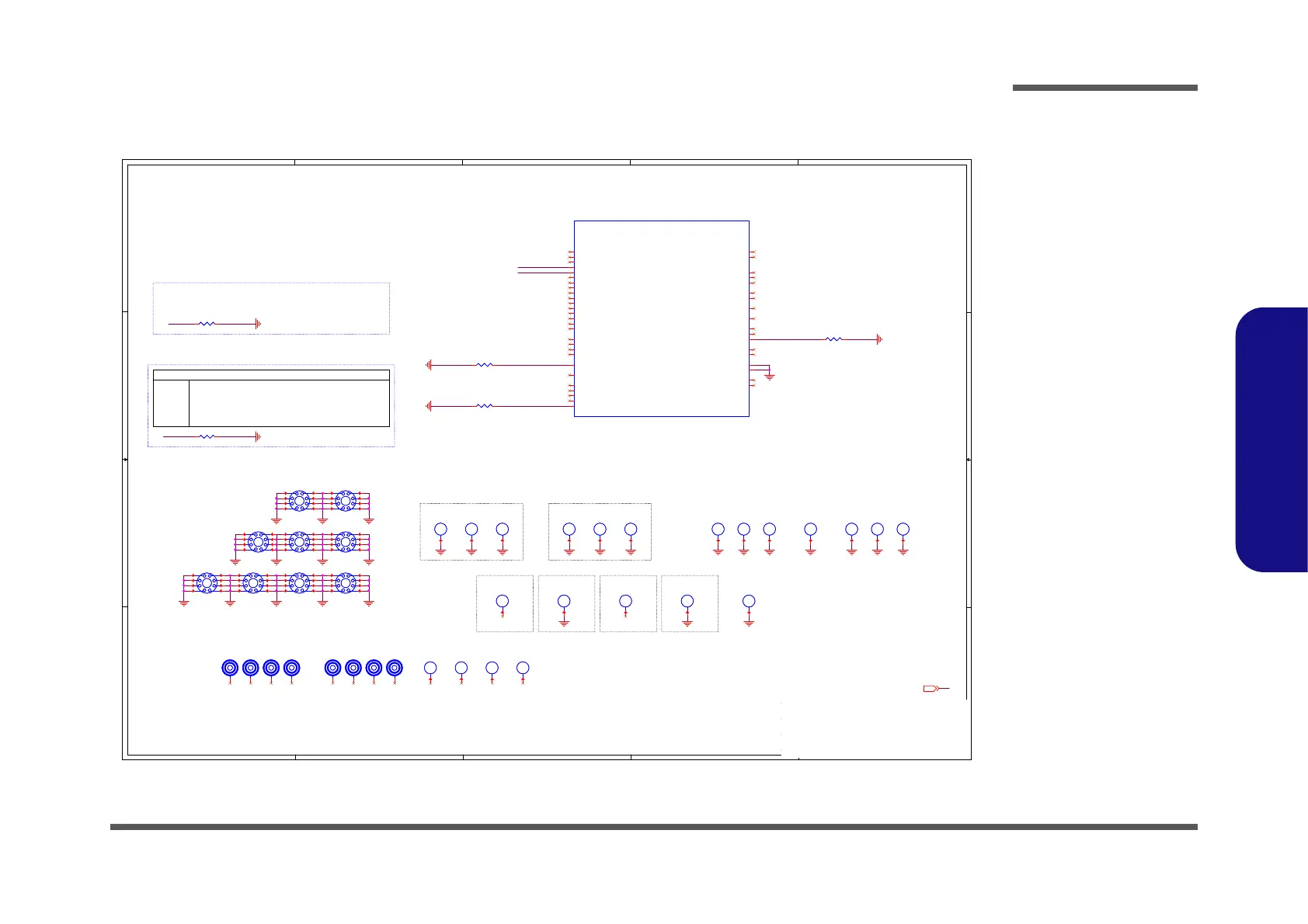

[12] BROADWELL ULT CFG,RSVD

A3

12 39W ednesday, July 16, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

Title

Size Document Number Rev

Date: Sheet

of

1.0

[12] BROADWELL ULT CFG,RSVD

A3

12 39W ednesday, July 16, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

Title

Size Document Number Rev

Date: Sheet

of

1.0

[12] BROADWELL ULT CFG,RSVD

A3

12 39W ednesday, July 16, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

1

H19

MTH10_0B8_0D2_8

1

H19

MTH10_0B8_0D2_8

2

3

4

5 6

7

8

9

M8

M-MARK

M8

M-MARK

H2

H8_0D2_8

H2

H8_0D2_8

H7

C4X2_4B7X5_4D4X2_4

H7

C4X2_4B7X5_4D4X2_4

M3

M-MARK

M3

M-MARK

1

H22

MTH8_0D2_8

1

H22

MTH8_0D2_8

2

3

4

5 6

7

8

9

R39149.9_1%_04 R39149.9_1%_04

M2

M-MARK

M2

M-MARK

H15

H6_0D3_7

H15

H6_0D3_7

H9

H8_0D2_8

H9

H8_0D2_8

R3118.2k_1%_04 R3118.2k_1%_04

M1

M-MARK

M1

M-MARK

H12

H8_0D2_8

H12

H8_0D2_8

1

H27

MTH6_0D2_2

1

H27

MTH6_0D2_2

2

3

4

5 6

7

8

9

H26

C111D111N

H26

C111D111N

M5

M-MARK

M5

M-MARK

R456 49.9_1%_04R456 49.9_1%_04

1

H21

MTH8_0D2_8

1

H21

MTH8_0D2_8

2

3

4

5 6

7

8

9

H11

H8_0D2_8

H11

H8_0D2_8

1

H10

MTH8_0D2_8

1

H10

MTH8_0D2_8

2

3

4

5 6

7

8

9

H18

H6_0D3_7

H18

H6_0D3_7

1

H14

MTH10_0B8_0D2_8

1

H14

MTH10_0B8_0D2_8

2

3

4

5 6

7

8

9

H1

C111D111N

H1

C111D111N

H17

H6_0D4_3

H17

H6_0D4_3

H5

C111D111N

H5

C111D111N

R392 1K_04R392 1K_04

H16

H6_0D4_3

H16

H6_0D4_3

H25

C111D111N

H25

C111D111N

1

H24

MTH8_0D2_8

1

H24

MTH8_0D2_8

2

3

4

5 6

7

8

9

RESERVED

HSW_ULT_DDR3L

19 OF 19

U20S

RESERVED

HSW_ULT_DDR3L

19 OF 19

U20S

CFG4

AA60

CFG5

Y62

CFG17

AA61

CFG18

U63

CFG7

Y60

CFG11

U60

RSVD_TP

AU63

RSVD_TP

C63

RSVD_TP

C62

RSVD_TP

L60

RSVD_TP

B51

RSVD_TP

A51

CFG10

V60

CFG9

V61

CFG8

V62

RSVD

N60

RSVD

Y22

RSVD

W23

RSVD

D58

RSVD

AV62

RSVD_TP

AV63

VSS

N21

VSS

P22

CFG19

U62

RSVD

R20

RSVD

P20

RSVD

J20

CFG3

AA63

CFG2

AC63

CFG1

AC62

CFG16

AA62

CFG15

T60

CFG14

T61

CFG_RCOMP

V63

RSVD

A5

RSVD

E1

RSVD

D1

TD_IREF

B12

RSVD

H18

PROC_OPI_RCOMP

AY15

CFG12

T63

CFG13

T62

CFG0

AC60

CFG6

Y61

RSVD

B43

H20

H6_0D3_7

H20

H6_0D3_7

S1

SQ-31G

S1

SQ-31G

H30

H6_0D2_8

H30

H6_0D2_8

H13

H6_0D4_3

H13

H6_0D4_3

H3

H8_0D2_8

H3

H8_0D2_8

M6

M-MARK

M6

M-MARK

H28

H6_0B4_7D3_8

H28

H6_0B4_7D3_8

1

H23

MTH8_0D2_8

1

H23

MTH8_0D2_8

2

3

4

5 6

7

8

9

M7

M-MARK

M7

M-MARK

R393 *1K_04R393 *1K_04

H29

H6_0B4_7D3_8

H29

H6_0B4_7D3_8

1

H6

MTH8_0D2_8

1

H6

MTH8_0D2_8

2

3

4

5 6

7

8

9

H4

H8_0D2_8

H4

H8_0D2_8

M4

M-MARK

M4

M-MARK

H8

H2_4B5_4D2_4

H8

H2_4B5_4D2_4

Loading...

Loading...