APPENDICES

Appendix 2 Special Register List

App

- 56

9

Device Explanation

10

CPU Module Processing

Time

11

Procedure for Writing

Program to CPU Module

Appendices

Index

*9: This applies to the CPU of function version B or later.

*13: This applies to the CPU with serial No. of first 5 digits "05032" or later.

TableApp.24 Special register

Number Name Meaning Explanation

Set by

(When set)

Corres-

ponding

ACPU

D9

Corresponding CPU

SD780

Remaining No.

of simultaneous

execution of

CC-Link

dedicated

instruction

0 to 32

• Stores the remaining number of simultaneous execution of the CC-Link

dedicated instructions.

UNew QnA

SD781

to

SD793

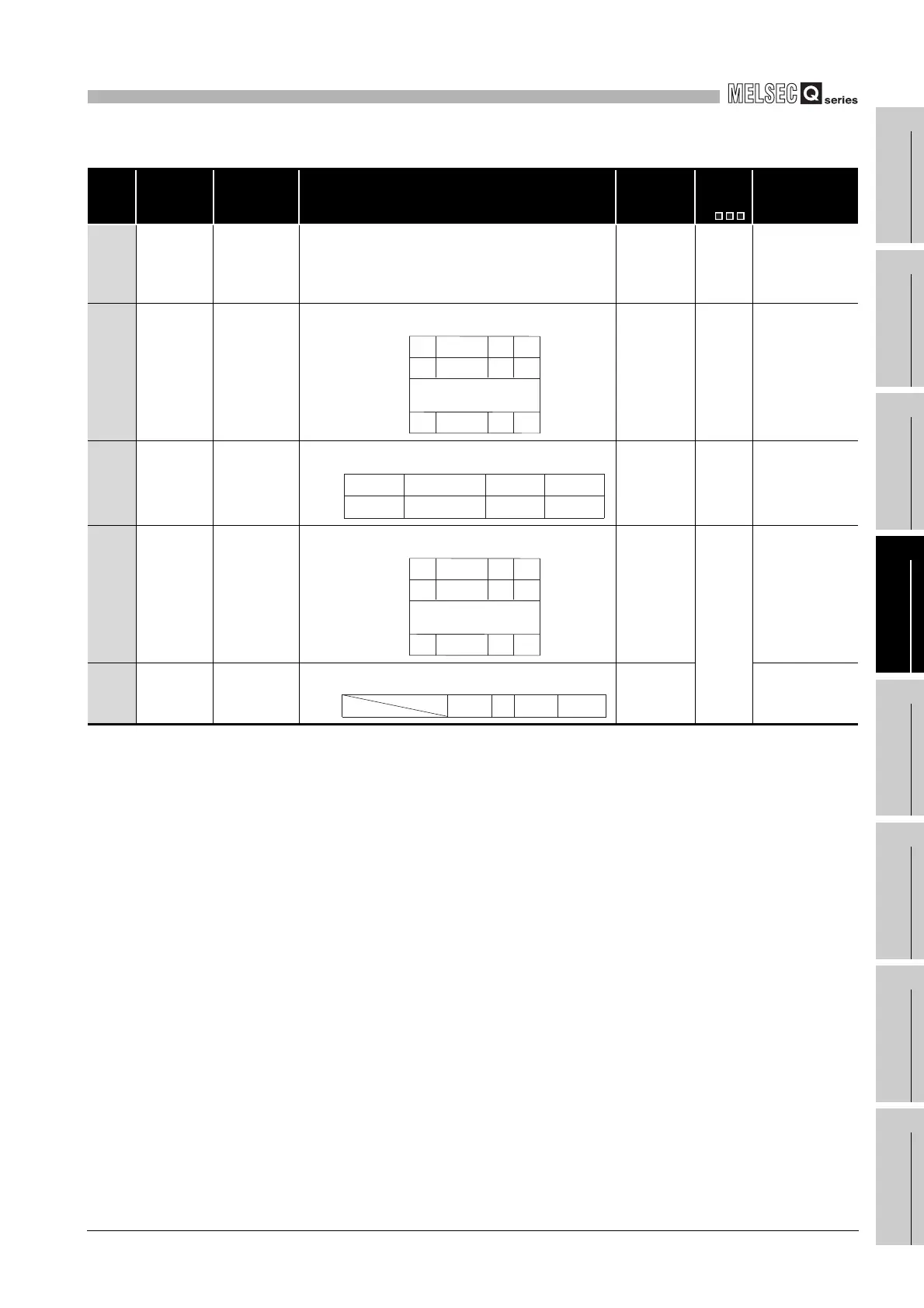

Mask pattern of

IMASK

instruction

Mask pattern

• Stores the mask patterns masked by the IMASK instruction as follows:

S (During

execution)

New

Qn(H)

QnPH

QnPRH

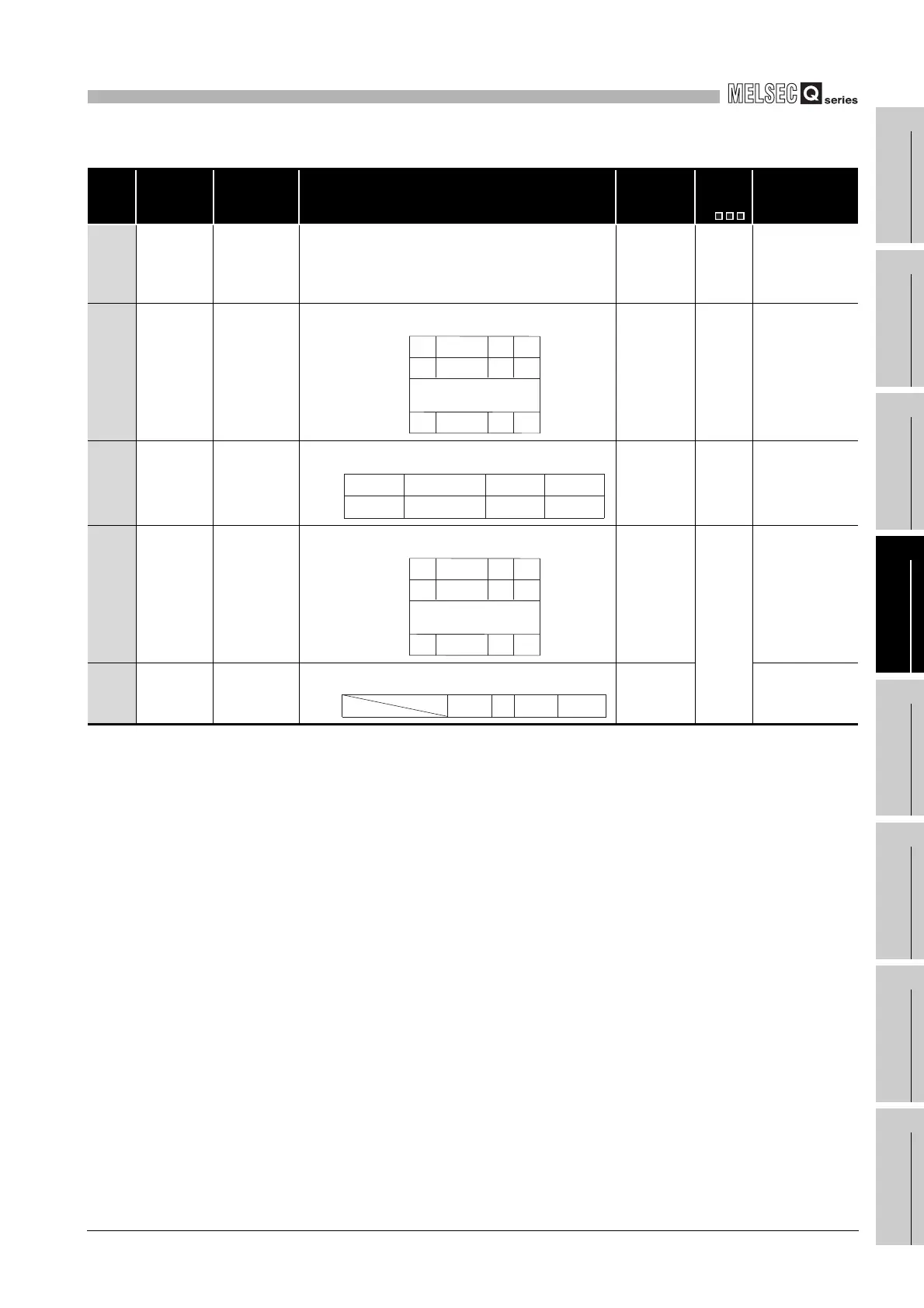

SD794

to

SD795

PID limit setting

(for incomplete

derivative)

0: Limit set

1: Limit not set

• Specify the limit of each PID loop as shown below.

UNew

Qn(H)

*13

QnPRH

SD781

to

SD785

Mask pattern of

IMASK

instruction

Mask pattern

• Stores the mask patterns masked by the IMASK instruction as follows:

S (During

execution)

New

Q00J/Q00/Q01

SD794

PID limit setting

(for inexact

differential)

0: With limit

1: Without limit

• Specify the limit of each PID loop as shown below.

U

Q00J/Q00/Q01

*9

SD781

SD782

SD793

l63

l49

l48

l79

l255

l65

l241

l64

l240

b15

b0

b1

to

to

to

to

SD794

SD795

b15

to

to

b1 b0

Loop16

Loop32

Loop2

Loop18

Loop1

Loop17

to

to

SD781

SD782

SD785

l63

l49

l48

l79

l127

l65

l113

l64

l112

b15 b0b1

to

to

to

SD794

b15

to

to

b1 b0

b7b8

Loop8 Loop2 Loop1

Loading...

Loading...