Maximum update rate

6

336 kS/s

Range ±10 V

Overrange operating voltage

Minimum 10.3 V

Typical 10.6 V

Maximum 10.9 V

Output impedance 0.4 Ω typical

Current drive ±3 mA/channel maximum

Protection Short-circuit to ground

Power-on state

7

0 V

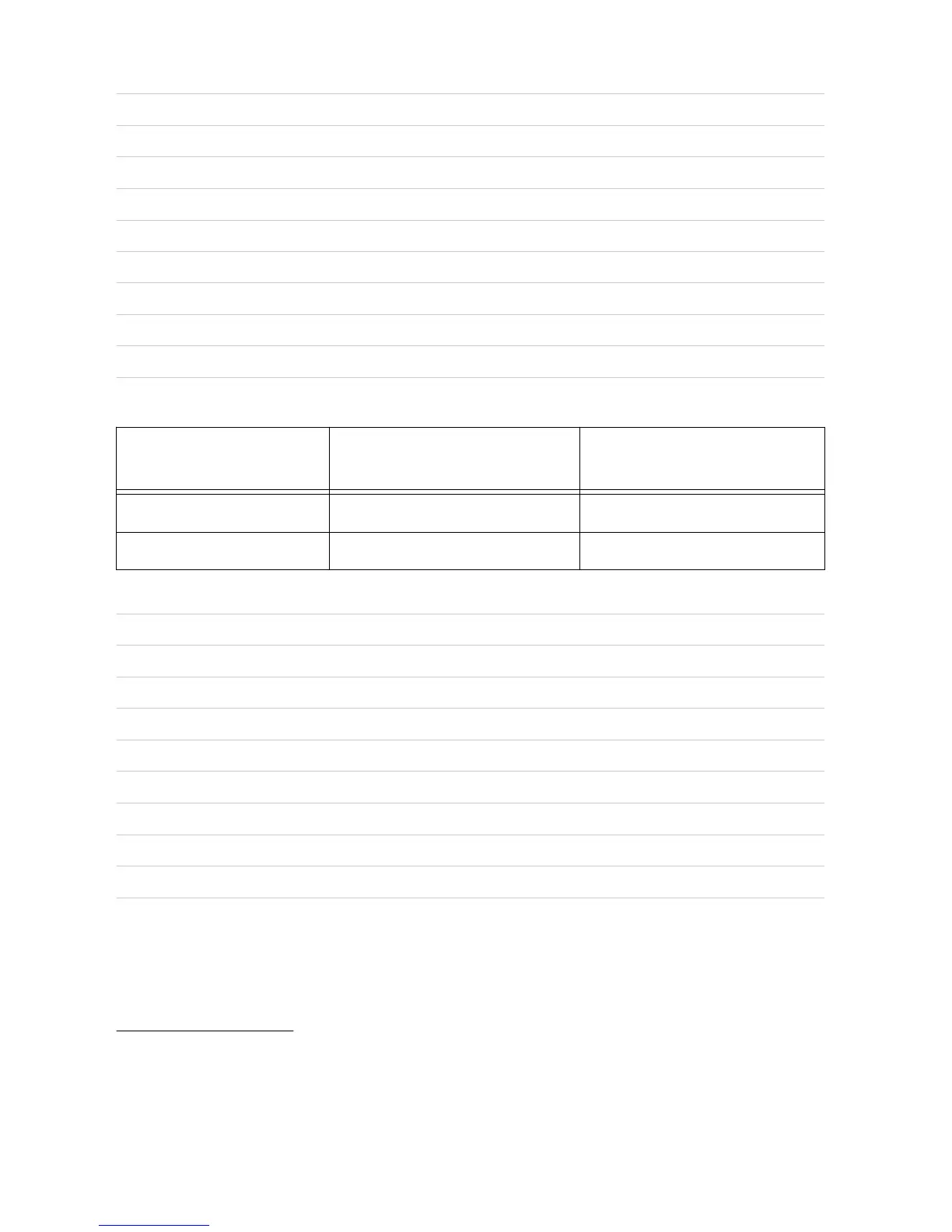

AO accuracy

Measurement Conditions Percent of Reading (Gain

Error)

Percent of Range (Offset

Error)

8

Typical (25 °C, ±5 °C) 0.09% 0.02%

Maximum (-40 to 85 °C) 0.50% 0.20%

Gain drift 23 ppm of reading/°C

Offset drift 5.4 ppm of range/°C

INL ±194 ppm of range, maximum

DNL ±16 ppm of range, maximum

Capacitive drive 1.5 nF, typical

Slew rate 3.7 V / μsec, typical

Settling time (100 pF load to 320 μV)

FS step 50 μs

2 V step 12 μs

0.2 V step 9 μs

6

This is the maximum update rate when running one AO channel in a loop with the FPGA top-level

clock set to 40 MHz.

7

When the analog output initializes, a voltage glitch occurs for about 20 μs, peaking at 1.3 V,

typical.

8

Range is 5 V.

NI sbRIO-9627 Specifications | © National Instruments | 9

Loading...

Loading...