B-38 | ni.com

Appendix B Timing Diagrams

Example of the General Case

Calculate the setup and hold time requirements when the Gate and Source come from PFI lines

and the Gate is used in level mode.

Note This example shows how we determine the setup and hold times for the PFI

to PFI example above (first case) using level gating.

Setup

To calculate the setup time, subtract the Source delay from the Gate delay. Use maximum

delays.

Hold

To calculate the hold time, subtract the Gate delay from the Source delay. Use minimum delays.

Output Delays

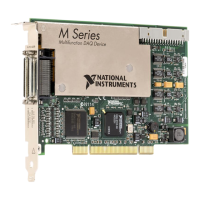

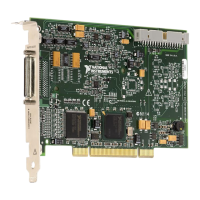

Refer to the Figure B-41 for the M Series counter/timer circuitry.

Gate Delay

PFI to PFI_i 22.0 ns

PFI_i to Selected Gate 6.0 ns

Selected Gate to Count Enable (Level) 18.0 ns

Count Enable Setup Time + 1.5 ns

47.5 ns

Source Delay

PFI to PFI_i 18.2 ns

PFI_i to Selected Source + 21.0 ns

39.2 ns

T

Setup

> 47.5 ns – 39.2 ns = 8.3 ns

Gate Delay

PFI to PFI_i 5.2 ns

PFI_i to Selected Gate 1.0 ns

Selected Gate to Count Enable (Level) 6.0 ns

Count Enable Hold Time + 0.0 ns

12.2 ns

Source Delay

PFI to PFI_i 6.2 ns

PFI_i to Selected Source + 8.0 ns

14.2 ns

T

Hold

> 14.2 ns – 12.2 ns = 2.0 ns

Loading...

Loading...