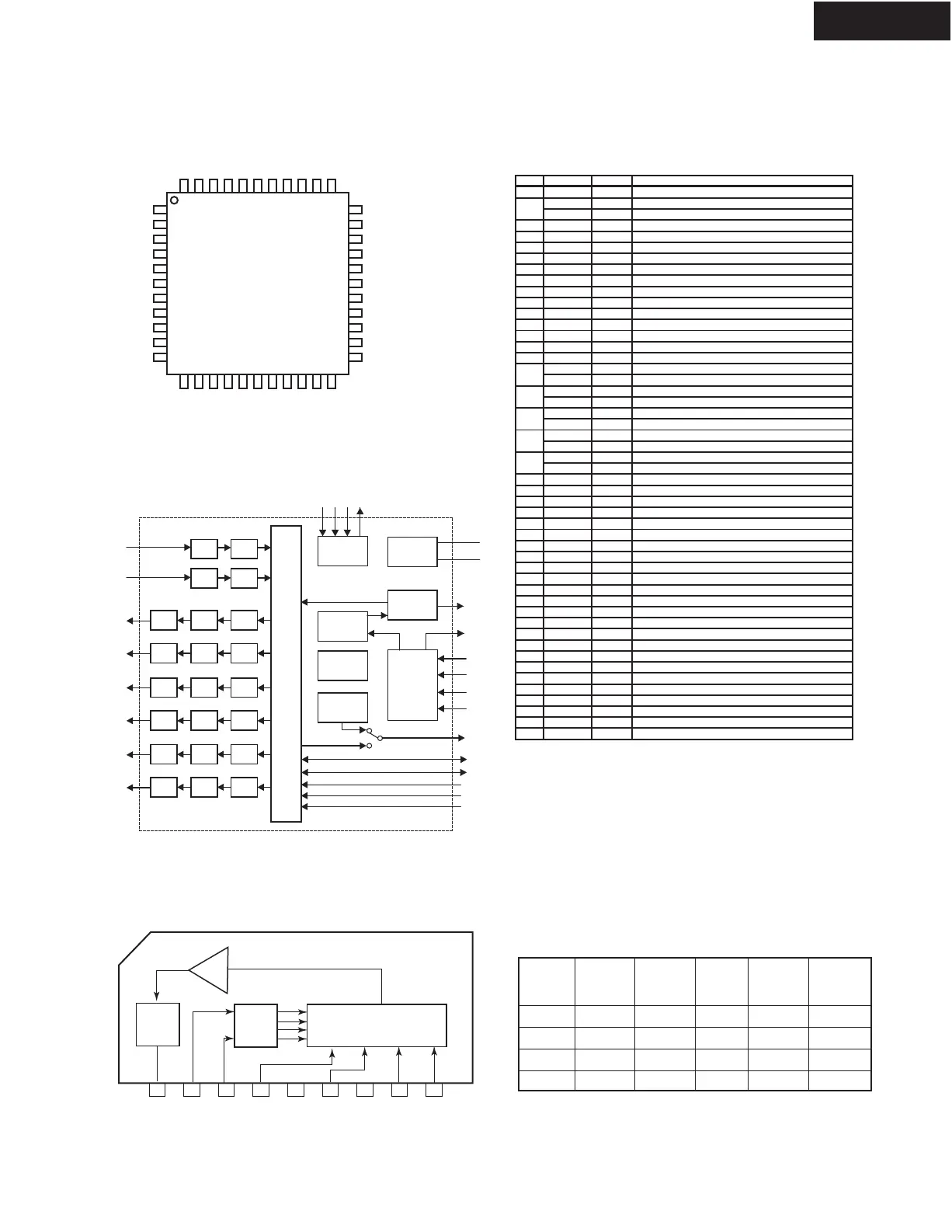

Pin Layout

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

33

32

31

30

29

28

27

26

25

24

23

44

43

42

41

40

39

38

37

36

35

34

AK4586VQ

Top View

XTO

XTI/EXTCLK

DVDD

DVSS

TVDD

TX

MCKO

LRCK

BICK

SDTO

SDTI1

SDTI2

SDTI3

INT0

INT1

CAD1/CDTO

SDA/CDT1

SCL/CCLK

CAD0/CSN

DZF2/OVF

AVSS

AVDD

RIN

LIN

ROUT1

LOUT1

ROUT2

LOUT2

ROUT3

LOUT3

DZF1

VCOM

VREFH

PDN

RX1

I2C

RX2

TST

RX3

SLAVE

RX4

PVSS

R

PVDD

Audio

I/

F

LP

F

LP

F

DA

C

DA

TT

LP

F

DA

C

DA

TT

LP

F

DA

C

DA

TT

LP

FDAC

DA

TT

LP

FDAC

DA

TT

LOUT1

RO

UT1

LOUT

2

RO

UT2

LOUT

3

RO

UT3

DAC

DATT

AK4586VQ

ADC

HP

F

AD

C

HP

F

RIN

LI

N

SDTI1

SDTI2

SDTI

3

MCLK

SDOUT

SDIN1

SDIN2

SDI

N3

BICK

LRCK

Input

Selector

Clock

Generator

X'tal

Oscillator

uP I/F

Clock

Recovery

DEM

SDTO

XTI

XTO

M

CKO

TX

RX1

RX2

RX3

RX4

CSN

CCLK

CDTI

CDTO

DAIF

Decoder

No. Name I/O Descri

tion

1XTO O Cr

stal oscillator out

ut

in

XTI I Cr

stal oscillator in

ut

in

EXTCLK I Master clock in

ut

in

3 TVDD - Power su

l

in for out

ut buffer. 2.7V to 5.5V

4 DVSS - Di

ital

round

in

5 DVDD - Power su

l

in for di

ital section. 4.5V to 5.5V

6 TX O Transmitter channel out

ut

in

7 MCKO O Master clock out

ut

in

8 LRCK I/O In

ut/Out

ut channel clock

in

9 BICK I/O Audio serial data clock

in

10 SDTO O Audio serial data out

ut

in

11 SDTI1 I Audio serial data in

ut

in for DAC1

12 SDTI2 I Audio serial data in

ut

in for DAC2

13 SDTI3 I Audio serial data in

ut

in for DAC3

14 INT0 O Interru

ter

in 0

15 INT1 O Interru

ter

in 1

CDTO O Control data out

ut

in

Serial mode

CADI I Chi

address

in 1

Bus mode

CDTI I Control data in

ut

in

Serial mode

SDA I/O Control data in

ut/out

ut

in

Bus mode

CCLK I Control data clock

in

Serial mode

SCL I Control data clock

in

Bus mode

CSN I Chi

select

in

Serial mode

CAD0 I Chi

address

in 0

Bus mode

DZF2 O Zero in

ut detection

in 2

OVF O Overflow detection

in for analo

in

ut

21 AVSS - Analo

round

in

22 AVDD - Power su

l

in for analo

section. 4.5V to 5.5V

23 VREFH I Reference volta

e in

ut

in, AVDD

24 VCOM O Common volta

e out

ut

in, AVDD/2

25 DZF1 O Zero in

ut detection

in 1

26 LOUT3 O DAC 3 left channel analo

out

ut

in

27 ROUT3 O DAC 3 ri

ht channel analo

out

ut

in

28 LOUT2 O DAC 2 left channel analo

out

ut

in

29 ROUT2 O DAC 2 ri

ht channel analo

out

ut

in

30 LOUT1 O DAC 1 left channel analo

out

ut

in

31 ROUT1 O DAC 1 ri

ht channel analo

out

ut

in

32 LIN I Left channel analo

in

ut

in

33 RIN I Ri

ht channel analo

in

ut

in

34 PVDD - PLL

ower su

l

in. 4.5V to 5.5V

35 R - External resistor connection

in

36 PVSS - PLL

round

in

37 RX4 I Receiver channel in

ut

in 4

38 SLAVE I Slave mode

in

39 RX3 I Receiver channel in

ut

in 3

40 TST I Test

in

41 RX2 I Receiver channel in

ut

in 2

42 I2C I Serial control mode select

in. Serial at H.

43 RX1 I Receiver channel in

ut

in 1

44 PDN I Power down and reset

in

19

20

2

16

17

18

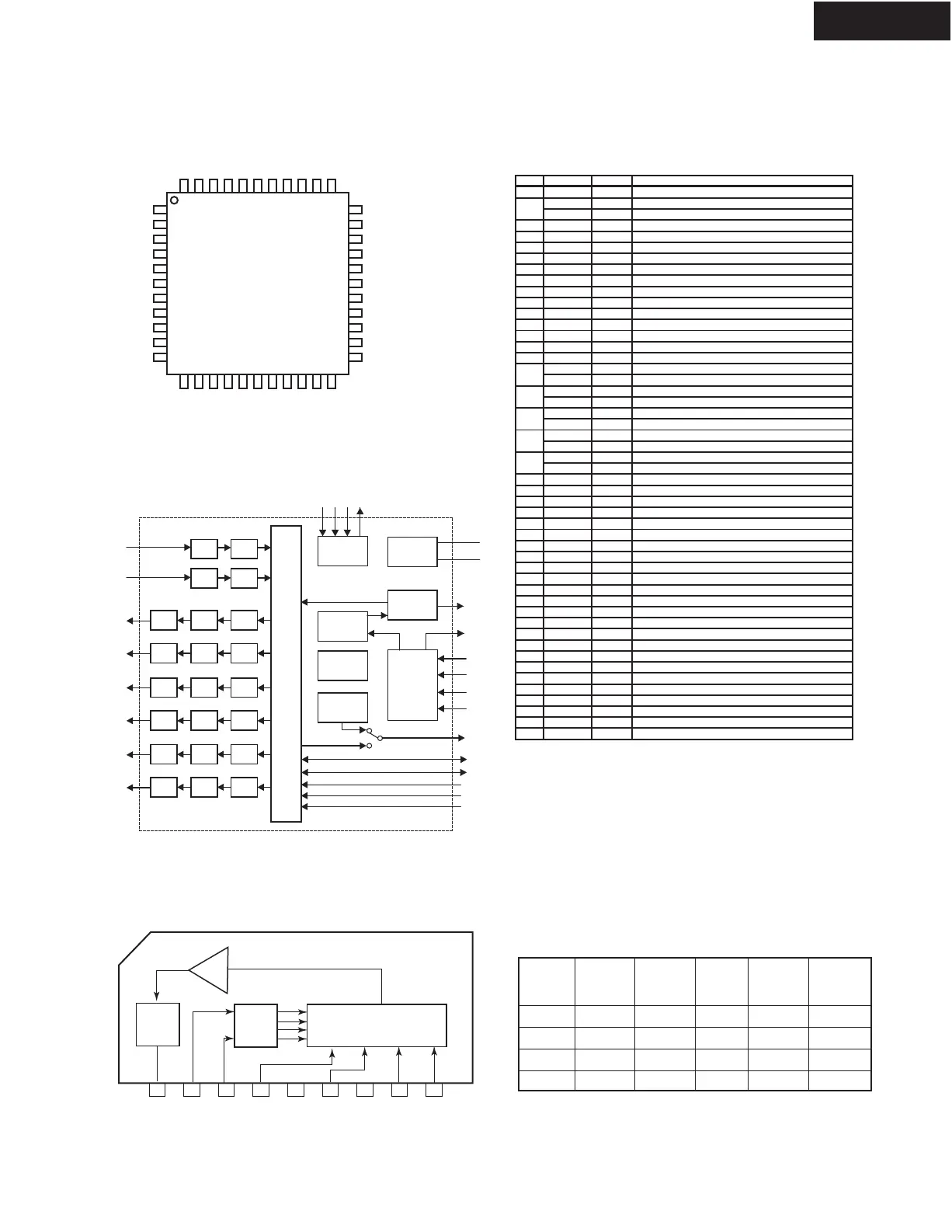

Block diagram

driver

control

6dB

amp.

video switch

(4 input 1 output)

123456789

VIDEO OUT A B VIN1 GND VIN2 VCC VIN3 VIN4

S2

(2 pin)

H

L

H

L

S3

(3 pin)

H

H

L

L

VIN1

(4 pin)

ON

OFF

OFF

OFF

VIN2

(6 pin)

OFF

ON

OFF

OFF

VIN3

(8 pin)

OFF

OFF

ON

OFF

VIN4

(9 pin)

OFF

OFF

OFF

ON

LA7956(Video Switch)

HT-R510

AK4586VQ(96kHz 6ch CODEC)

IC BLOCK DIAGRAMS AND DESCRIPTIONS

Loading...

Loading...