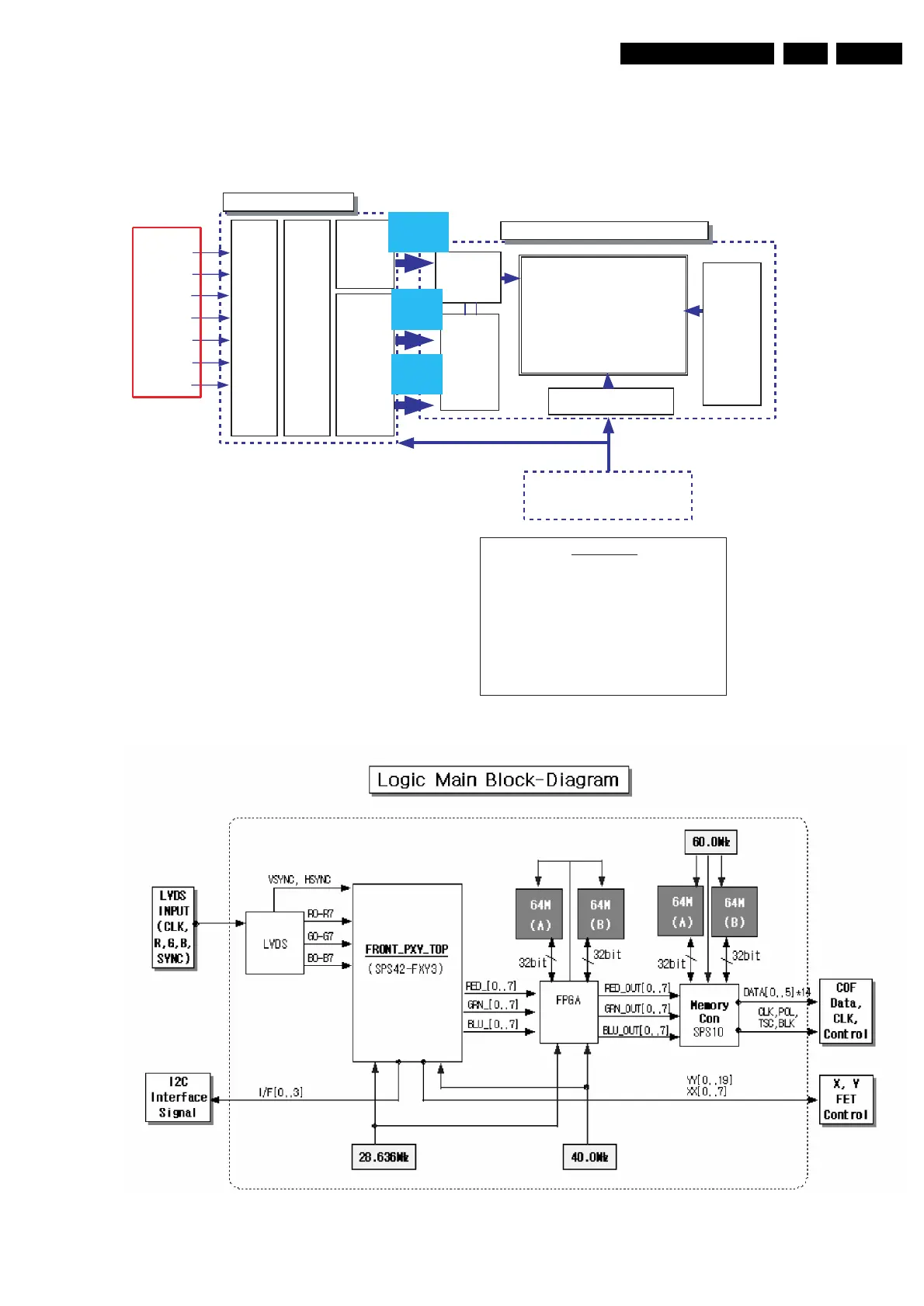

Block Diagrams, Testpoint Overview, and Waveforms

EN 27S/SD/HD 3.1 PDP 6.

6. Block Diagrams, Testpoint Overview, and Waveforms

6.1 Block Diagram for Logic circuit

42" SDv2

42" SDv3

852× 480 Pixels

852× 3× 480 Cells

P

Y

u

l

s

e

G

et

are

n

o

r

oRw

rDive

r

VsVa

V5

Vs ync

Enable

Hsync

DCLK

ARDM

Display

Data

i

rDver

T

imi gnCt

n

o

r

oll

e

r

Driver

Timing

Scan

Timing

Vdd

DATA_R

8Bits

Column Driver

Reference

-V3.3 :

-V5 :

-Vdd :

-Va :

-Vs :

-Vsc :

-Ve :

-Vset :

LOGIC CONTROL

DRIVER CIRCUIT & PANEL

DATA_G

8Bits

DATA_B

8Bits

In tupDataProcsesor

aD

t

ao

C

nt or ller

P

X

ulse

eG

n

era

to

r

Vset Vsc

Ve V3.3

LVDS

Voltage for LOGIC Control

Voltage for COF driver

Voltage for FET driver

Voltage for address pulse

Voltage for sustain driver

Voltage for scan pulse

Voltage for X ramppulse

Voltage for Y ramppulse

Loading...

Loading...