Block Diagrams, Testpoint Overview, and Waveforms

EN 29S/SD/HD 3.1 PDP 6.

50" HDv3

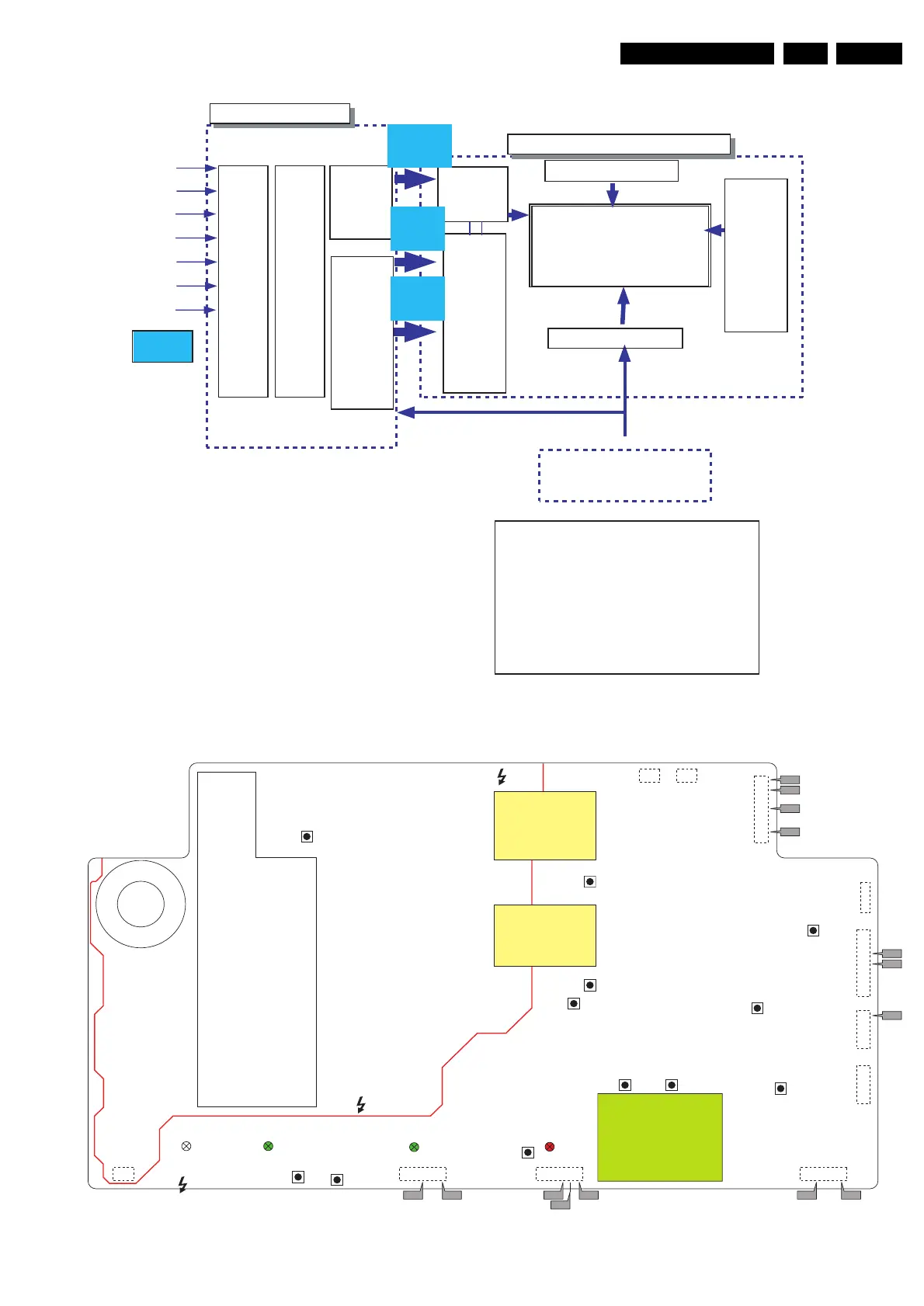

6.2 PSU Board diagram

42" SDv2

- Vcc : Voltage for Logic Control

- Vdd : Voltage for FET driver

- Va : Voltage for address pulse

- Vsc_l

: Voltage sustain low

- Vscan : Voltage for scan high

- Vb : Voltage for X bias

- Vset : Voltage for Y ramp pulse

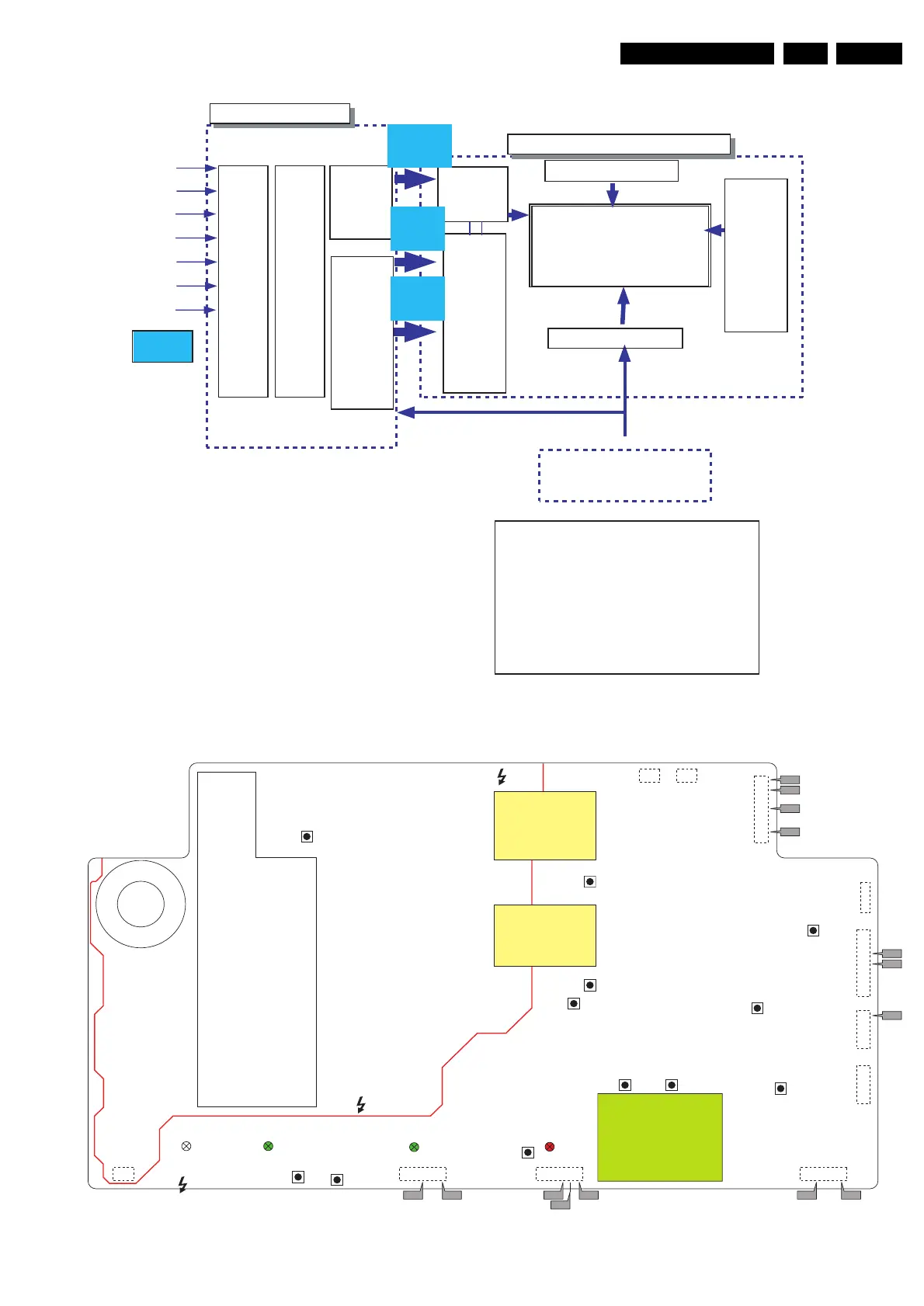

Reference

1366× 768 Pixels

1366× 3× 768 Cells

YPulse

Generator

Row

Driver

Vsync

Enable

Hsync

DCLK

DRAM

Display

Data

Driver

Timing Controller

Driver

Timing

Scan

Timing

VsVaVcc Vdd

DATA_R

8(9)Bits

Column Driver

LOGIC CONTROL

DRIVER CIRCUIT & PANEL

DATA_G

8(9)Bits

DATA_B

8(9)Bits

Input Data Processor

Data Controller

XPulse

Generator

Vset

Vscan

Vb

LVDS

Interface

Column Driver

Vsc_l

CL 36532011_009.eps

050303

COLDHOT

COLD

HOT

13

8004

GREEN

VS

8001

13

8005

13

8006

1510

8009

13413

8002

1812

5

1

5

10

1

4

5

1

1

9

8001

8011

Protection

Board

8010

8008

8003

P7 P6 P2 P1

P4

P5 P3

P12

P13

9

1

2

5

8

8007

P8

P9

P10

P11

P14

GREEN

8002

GREEN

8003

RED

8004

VE

VA

Vcc

VSCAN

VSET

8V6 VFAN

DV5

PFC

3V3_VSB_S

5V_STBY_S

COLD HOT

Loading...

Loading...