Serie PSS CPU/PSS1 CPU

2 Bedienungsanleitung

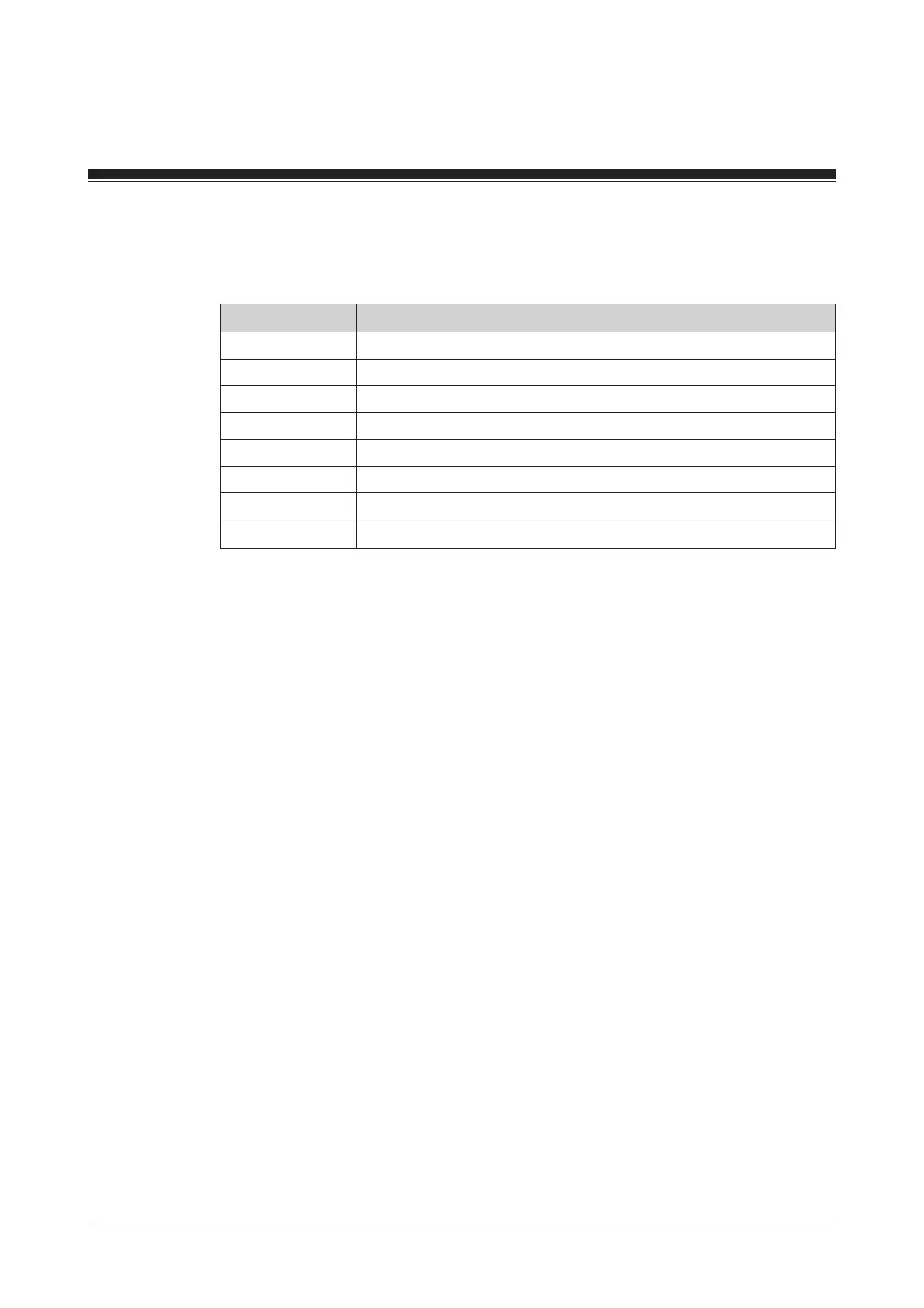

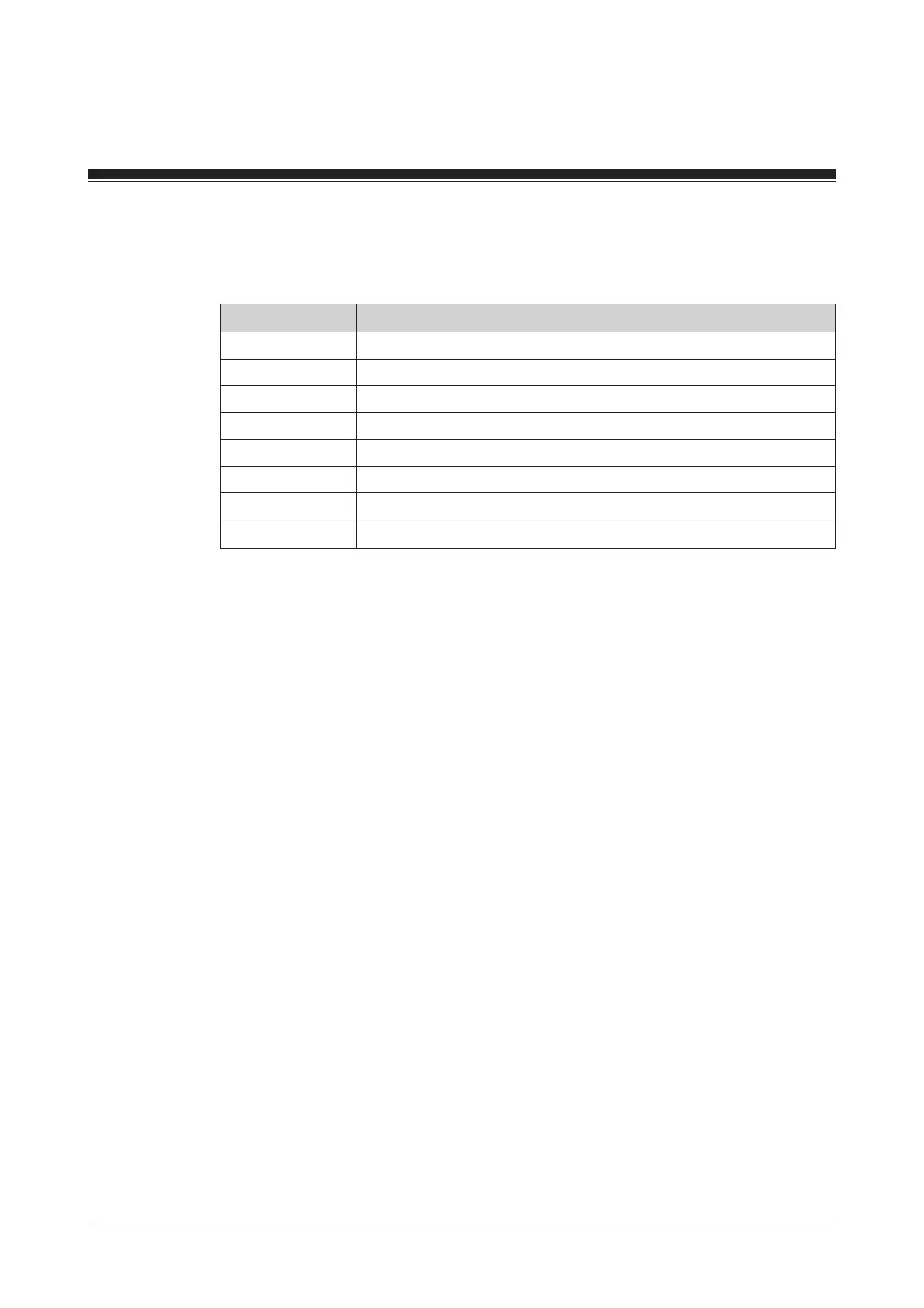

Übersicht

Die CPU-Baugruppe ist die Zentraleinheit der Sicherheitssteuerung.

CPU Sicherheitssteuerung

PSS CPU PSS 3000

PSS1 CPU PSS 3100

PSS CPU 2 PSS 3000

PSS1 CPU 2 PSS 3100

PSS SB CPU PSS SB 3000 (PSS 3000 mit SafetyBUS p-Schnittstelle)

PSS1 SB CPU PSS SB 3100 (PSS 3100 mit SafetyBUS p-Schnittstelle)

PSS SF CPU PSS SF 3000 (PSS 3000 mit Gruppenabschaltung)

PSS1 SF CPU PSS SF 3100 (PSS 3100 mit Gruppenabschaltung)

Die CPU steuert die zentralen sowie ggf. die dezentralen Peripherie-

baugruppen an. Sie bearbeitet und speichert das Anwenderprogramm und

die variablen Daten. Die CPU ist unterteilt in einen Fail-safe- und einen

Standard-Teil.

Die sicherheitsgerichteten Aufgaben werden im Fail-safe-Teil der CPU

bearbeitet. Der Fail-safe-Teil ist dreikanalig aufgebaut, d. h. drei diver-

sitäre Prozessoren bearbeiten unabhängig voneinander das Anwender-

programm.

Der Standard-Teil ist einkanalig aufgebaut. Er bearbeitet alle nicht sicher-

heitsrelevanten Aufgaben.

Ein vierstelliges Display und mehrere LED informieren über den Status der

Sicherheitssteuerung und zeigen Fehler an.

Die CPU stellt folgende Schnittstellen zur Verfügung:

• PSS CPU, PSS1 CPU, PSS SB CPU, PSS1 SB CPU, PSS SF CPU,

PSS1 SF CPU:

- Programmiergeräteschnittstelle RS 485

- Anwenderschnittstelle RS 232

• PSS CPU 2, PSS1 CPU 2:

- Programmiergeräteschnittstelle RS 232 / RS 485

- Anwenderschnittstelle RS 232 / RS 485

• Schnittstelle zu den zentralen Peripheriebaugruppen (Fail-safe- und

Standard-Baugruppen)

• PSS SB CPU: SafetyBUS p-Schnittstelle zu den dezentralen Peripherie-

baugruppen (Fail-safe-Baugruppen) bzw. zur dezentralen Vernetzung

mehrerer Steuerungssysteme

Loading...

Loading...