Instruction Reference Manual 77

Description

Resets bit b (any of the bits 0, 1, 2, 3, 4, 5, 6, or 7) of the data whose address is:

• heldinwordregisterHL, or

• the sum of the data in index register IX and a displacement d,or

• the sum of the data in index register IX and a displacement d.

The bit is reset by performing a logical AND between the selected bit and its complement.

RES b,(HL)

RES b,(IX+d)

RES b,(IY+d)

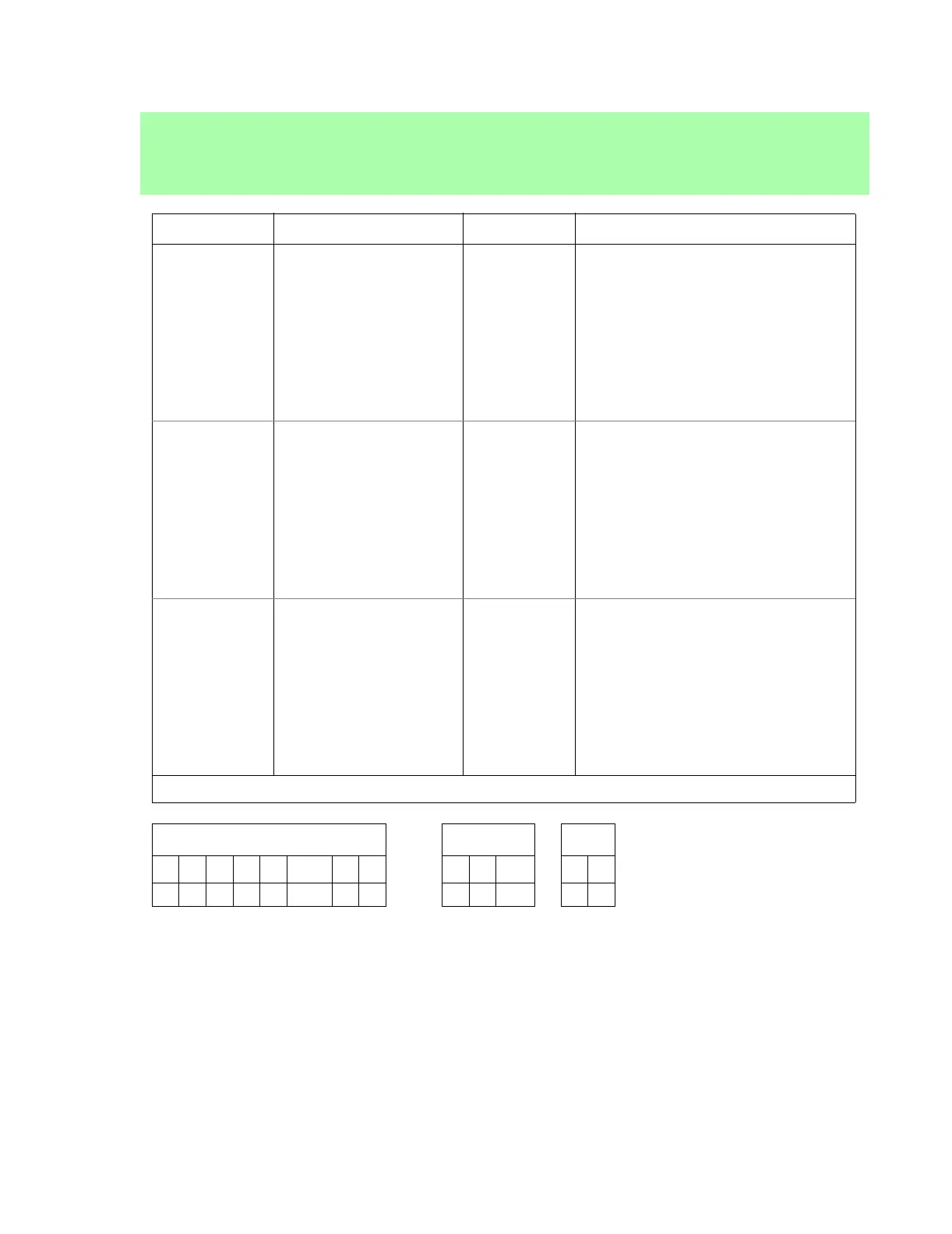

Opcode Instruction Clocks Operation

——

CB 86

CB 8E

CB 96

CB 9E

CB A6

CB AE

CB B6

CB BE

RES b,(HL)

RES bit 0,(HL)

RES bit 1,(HL)

RES bit 2,(HL)

RES bit 3,(HL)

RES bit 4,(HL)

RES bit 5,(HL)

RES bit 6,(HL)

RES bit 7,(HL)

10*

10*

10*

10*

10*

10*

10*

10*

10*

(HL) = (HL) & ~bit b

(HL) = (HL) & ~bit 0

(HL) = (HL) & ~bit 1

(HL) = (HL) & ~bit 2

(HL) = (HL) & ~bit 3

(HL) = (HL) & ~bit 4

(HL) = (HL) & ~bit 5

(HL) = (HL) & ~bit 6

(HL) = (HL) & ~bit 7

——

DD CB d 86

DD CB d 8E

DD CB d 96

DD CB d 9E

DD CB d A6

DD CB d AE

DD CB d B6

DD CB d BE

RES b,(IX+d)

RES bit 0,(IX+d)

RES bit 1,(IX+d)

RES bit 2,(IX+d)

RES bit 3,(IX+d)

RES bit 4,(IX+d)

RES bit 5,(IX+d)

RES bit 6,(IX+d)

RES bit 7,(IX+d)

13**

13**

13**

13**

13**

13**

13**

13**

13**

(IX + d)=(IX+d)&~bit

(IX + d) = (IX + d)&~bit0

(IX + d) = (IX + d)&~bit1

(IX + d) = (IX + d)&~bit2

(IX + d) = (IX + d)&~bit3

(IX + d) = (IX + d)&~bit4

(IX + d) = (IX + d)&~bit5

(IX + d) = (IX + d)&~bit6

(IX + d) = (IX + d)&~bit7

——

FD CB d 86

FD CB d 8E

FD CB d 96

FD CB d 9E

FD CB d A6

FD CB d AE

FD CB d B6

FD CB d BE

RES b,(IY+d)

RES bit 0,(IY+d)

RES bit 1,(IY+d)

RES bit 2,(IY+d)

RES bit 3,(IY+d)

RES bit 4,(IY+d)

RES bit 5,(IY+d)

RES bit 6,(IY+d)

RES bit 7,(IY+d)

13**

13**

13**

13**

13**

13**

13**

13**

13**

(IY + d)=(IY+d)&~bit

(IY + d) = (IY + d)&~bit0

(IY + d) = (IY + d)&~bit1

(IY + d) = (IY + d)&~bit2

(IY + d) = (IY + d)&~bit3

(IY + d) = (IY + d)&~bit4

(IY + d) = (IY + d)&~bit5

(IY + d) = (IY + d)&~bit6

(IY + d) = (IY + d)&~bit7

Clocking: *10 (2,2,1,2,3) **13 (2,2,2,2,2,3)

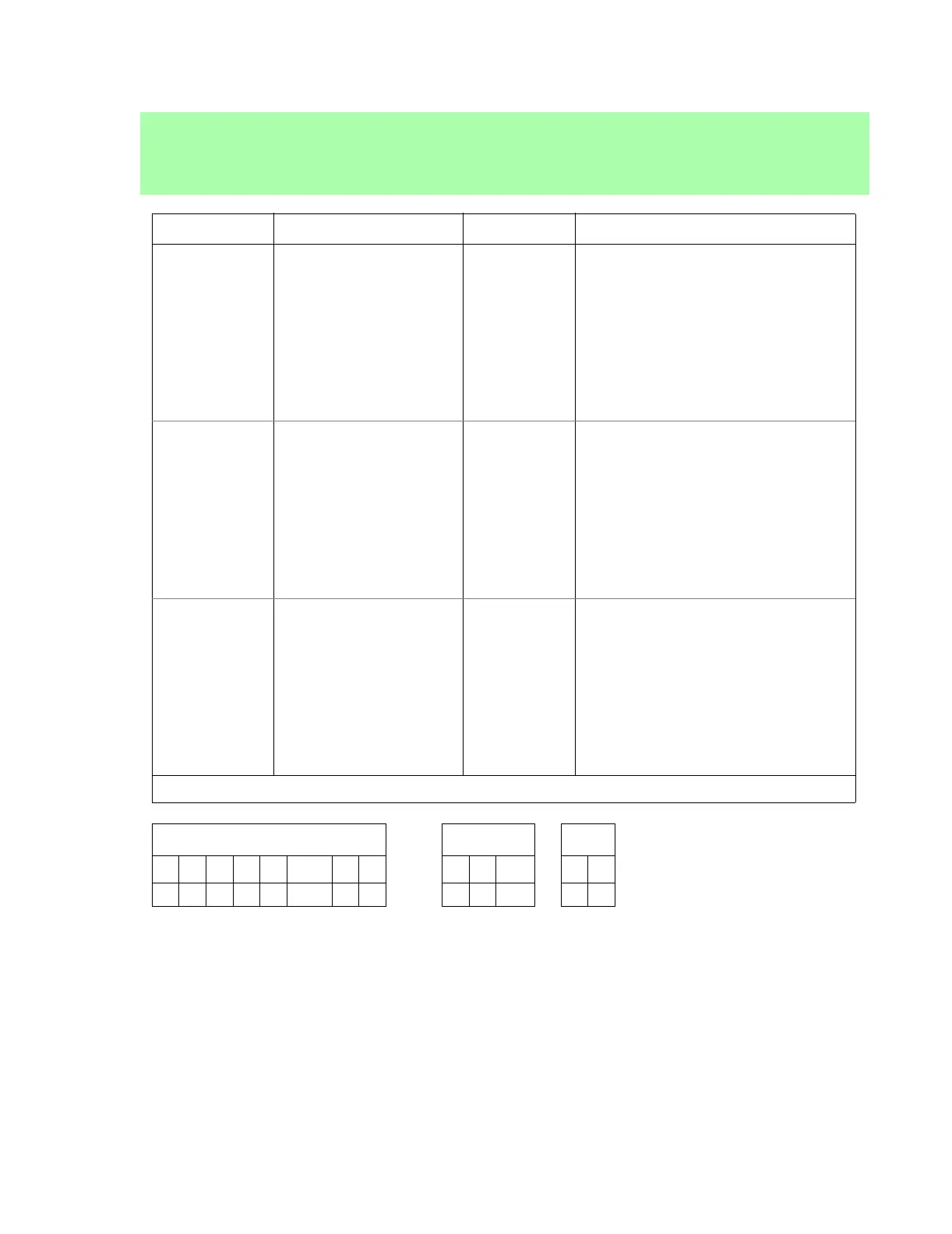

Flags ALTD I/O

S Z L/V C F R SP S D

- - - - •

Loading...

Loading...