Test

Device

(TDV)

General

Description

Format

(SI)

Condition Code

Interrupt

Action

Notes

Privileged

Instructions

• The contents of

the

general

register

specified

by

Bl

are

added to

the

Dl

field. The

resultant

sum identifies

the

channel

and

device to which

the

instruction

applies. These

are

specified by

bit

positions

21

through

31

of

the

sum. The I-field is

not

used

and

must

be zeros. The condition code

specifies

the

results

of

the

instruction.

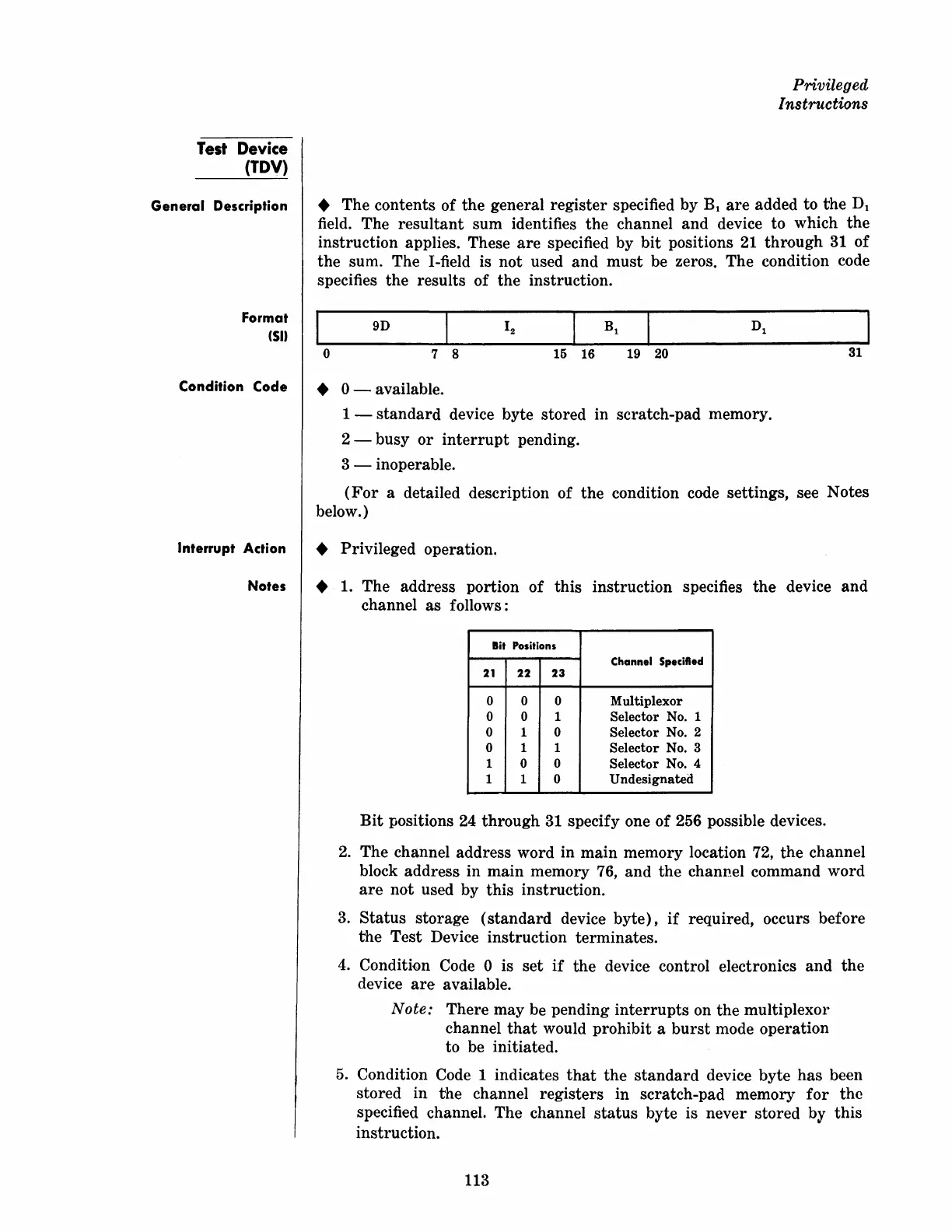

9D

o

7 8

16 16 19 20

31

• 0 - available.

1-

standard

device byte stored in scratch-pad memory.

2 - busy

or

interrupt

pending.

3 - inoperable.

(For

a detailed description of

the

condition code settings, see Notes

below.)

• Privileged operation.

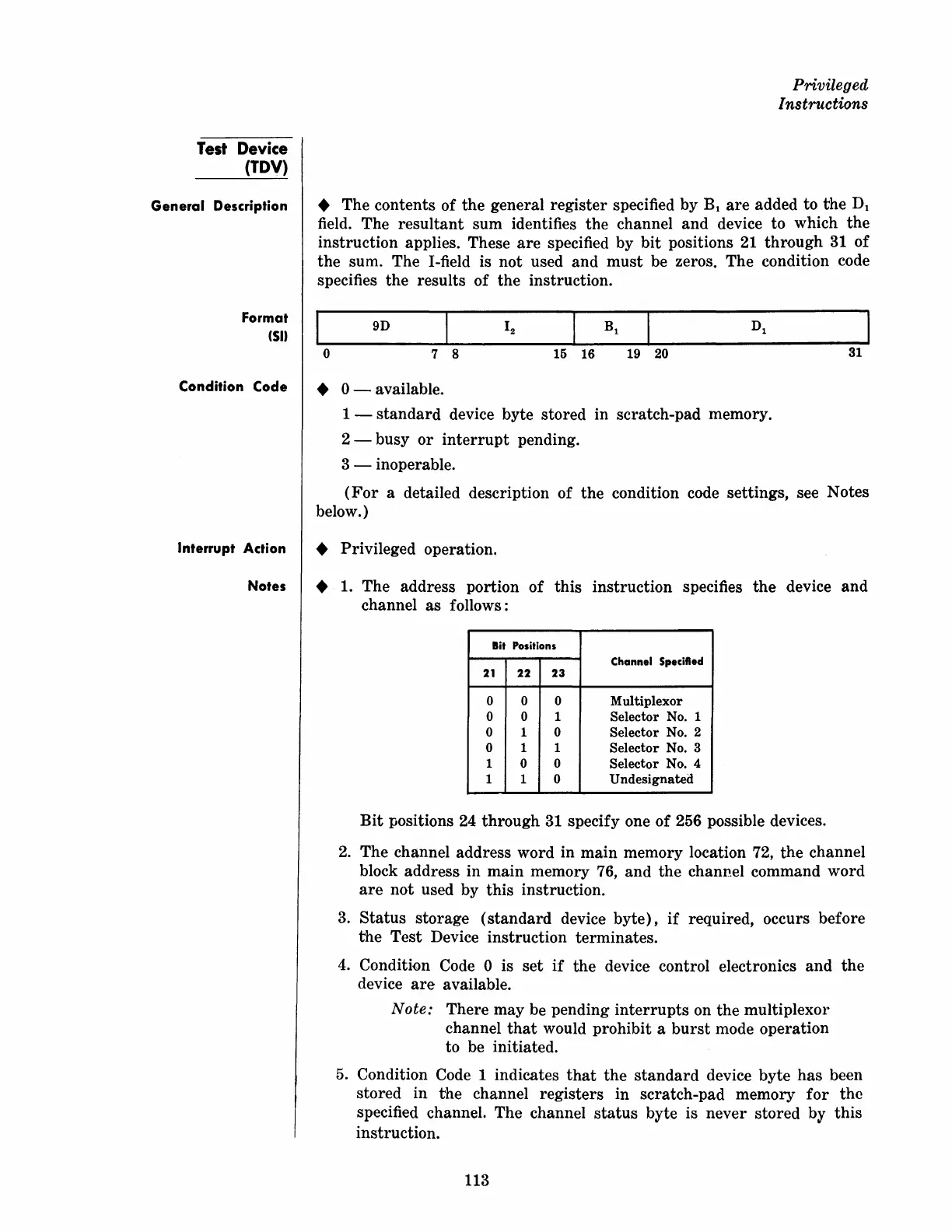

• 1.

The

address portion

of

this

instruction

specifies

the

device

and

channel

as

follows:

Bit

Positions

Channel

Specified

21

22 23

0 0 0

Multiplexor

0 0 1 Selector

No.1

0 1 0

Selector

No. 2

0 1 1

Selector

No. 3

1

0

0

Selector

No. 4

1

1 0

Undesignated

Bit

positions 24

through

31 specify one

of

256 possible devices.

2.

The

channel address word in

main

memory location 72,

the

channel

block address in

main

memory 76,

and

the

channel command

word

are

not

used

by

this

instruction.

3.

Status

storage

(standard

device

byte),

if

required, occurs before

the

Test

Device instruction terminates.

4.

Condition Code 0 is

set

if

the

device control electronics

and

the

device

are

available.

Note:

There

may

be pending

interrupts

on

the

multiplexor

channel

that

would prohibit a

burst

mode operation

to be initiated.

5.

Condition Code 1 indicates

that

the

standard

device

byte

has

been

stored

in

the

channel

registers

in scratch-pad memory

for

the

specified channel. The channel

status

byte is

never

stored by

this

instruction.

113

Loading...

Loading...