RTL8201(L)

2002-01-18 Rev.1.04

15

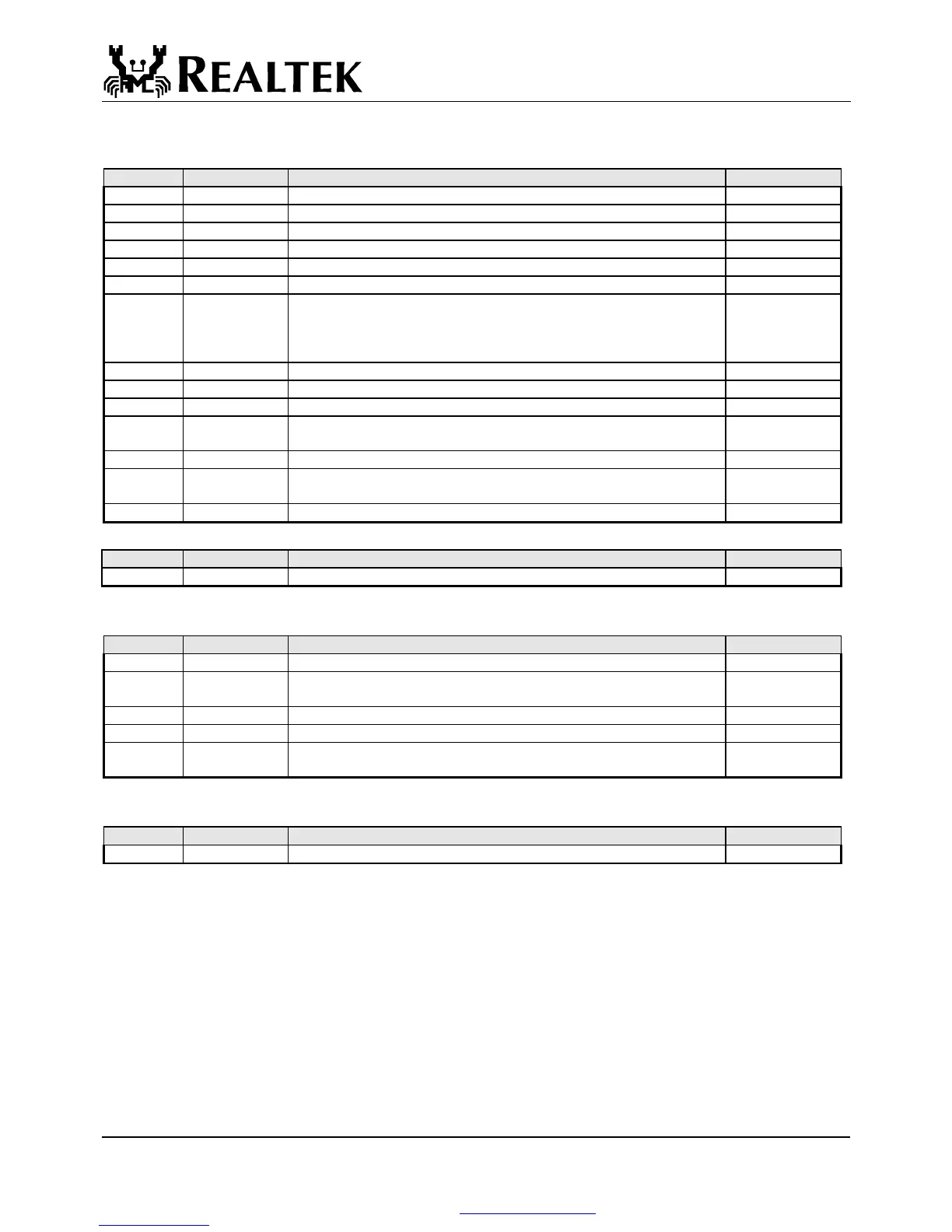

6.9 Register 17 Loopback, Bypass, Receiver Error Mask (LBREMR)

Address Name Description/Usage Default/Attribute

17:<15> RPTR Set to 1 to put the RTL8201(L) into repeater mode 0, RW

17:<14> BP_4B5B Assertion of this bit allows bypassing of the 4B/5B & 5B/4B encoder. 0, RW

17:<13> BP_SCR Assertion of this bit allows bypassing of the scrambler/descrambler. 0, RW

17:<12> LDPS Set to 1 to enable Link Down Power Saving mode 0, RW

17:<11> AnalogOFF Set to 1 to power down analog function of transmitter and receiver. 0, RW

17:<10> Reserved Ignore the results of this bit when read.

17:<9:8> LB<1:0> LB<1:0> are register bits for loopback control as defined below:

1) 0 0 for normal mode;

2) 0 1 for PHY loopback;

3) 1 0 for twister loopback

<0, 0>, RW

17:<7> F_Link_100 Used to logic force good link in 100Mbps for diagnostic purposes. 1, RW

17:<6:5> Reserved Ignore the results of these bits when read.

17:<4> CODE_err Assertion of this bit causes a code error detection to be reported. 0, RW

17:<3> PME_err Assertion of this bit causes a pre-mature end error detection to be

reported.

0, RW

17:<2> LINK_err Assertion of this bit causes a link error detection to be reported. 0, RW

17:<1> PKT_err Assertion of this bit causes a detection of packet errors due to 722 ms

time-out to be reported.

0, RW

17:<0> RWPara Parameter access enable, set 1 to access register 20~24 0, RW

6.10 Register 18 RX_ER Counter (REC)

Address Name Description/Usage Default/Attribute

18:<15:0> RXERCNT This 16-bit counter increments by 1 for each valid packet received. H’[0000], RW

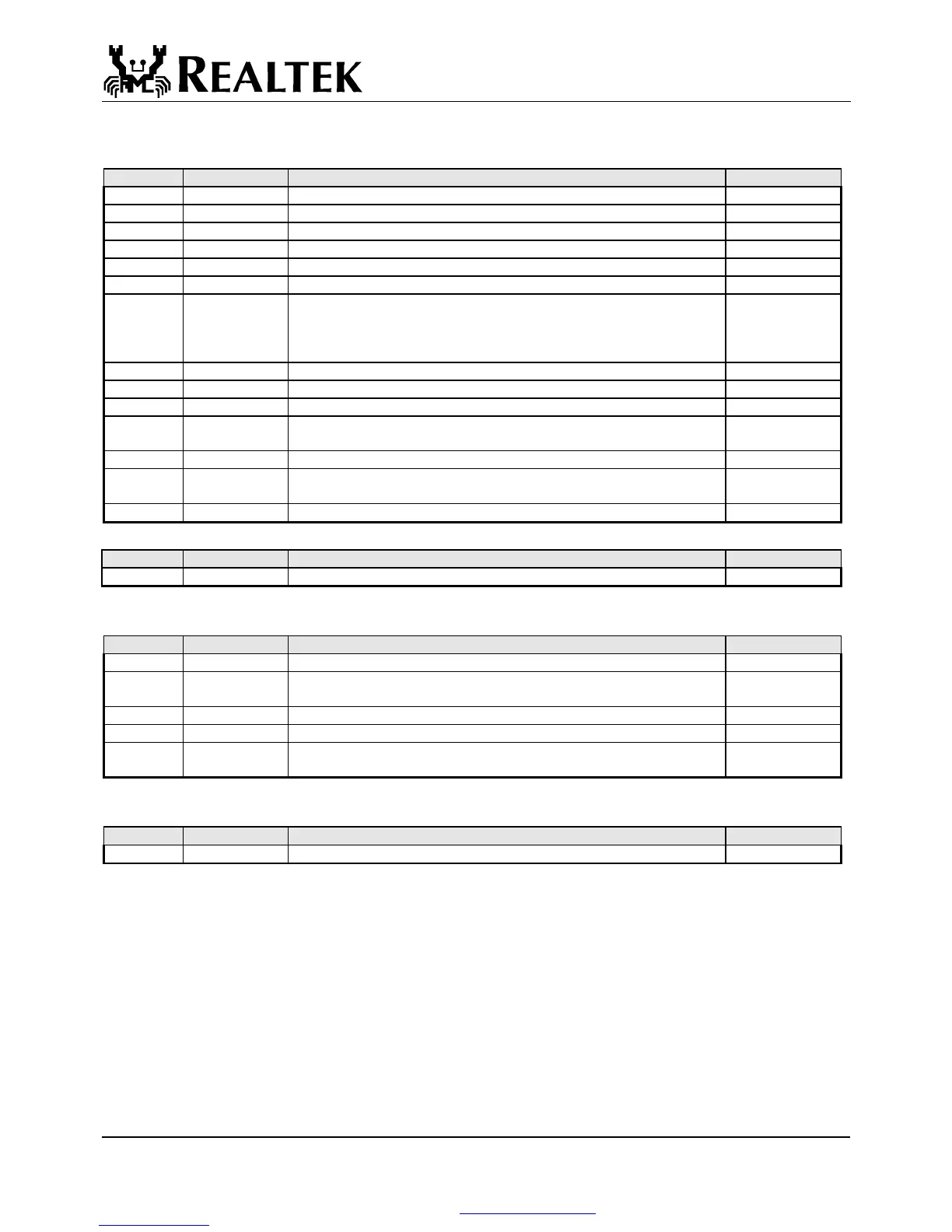

6.11 Register 19 10Mbps Network Interface Configuration

Address Name Description/Usage Default/Attribute

19:<15:6> Reserved Ignore the results of these bits when read.

19:<5> LD This bit is the active low TPI link disable signal. When low

TPIstilltransmit link pulses and TPI stays in good link state.

1, RW

19:<4:2> Reserved Ignore the results of these bits when read.

19:<1> HBEN Heart beat enable 1, RW

19:<0> JBEN 1: Enable jabber function

0: Disable jabber function

1, RW

6.12 Register 20 PHY 1_1

Address Name Description/Usage Default/Attribute

20:<15:0> PHY1_1 PHY 1 register (functions as RTL8139C<78>) R/W

Tel: +49(0)234-9351135 · Fax: +49(0)234-9351137 E-MAIL:info@cornelius-consult.de http://www.cornelius-consult.de

Loading...

Loading...