of 24

Jan.31.2020

[CC_I|goal_lmLogLegacy:1152] [I|goal_queuePoolBufsReq:777] fixed/temp = 2, 0

[CC_I|goal_lmLogLegacy:1152] [I|goal_queuePoolBufsReq:776] ID(35) requests buffers[1556]

[CC_I|goal_lmLogLegacy:1152] [I|goal_queuePoolBufsReq:777] fixed/temp = 1, 0

[CC_I|goal_lmLogLegacy:1152] [I|goal_taskCreate:74] creating task: Timer

[CC_I|goal_lmLogLegacy:1152] [I|goal_init:190] GOAL initialized

[CC_I|goal_lmLogLegacy:1152] [I|appl_setup:85] Chase Lights application started.

[CC_I|goal_lmLogLegacy:1152] [I|goal_memInitDone:128] fixed memory usage: 16020/196608 bytes

[CC_I|goal_lmLogLegacy:1152] [I|goal_memInitDone:129] fixed memory usage: (9%)

3.1.2 Run and debug Cortex A7 software from RAM with IAR Debugger

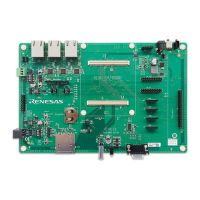

The steps are almost the same as the ones described in chapter 3.1.1. Reset the board by pressing SW9.

Follow the steps 1-4 from the previous chapter with the difference that you should open a Cortex A7 workspace

file in IAR EWARM (step 4):

YCONNECT-IT-RZN_V1.X\Software\ThreadX\rzn1\iar\x-ware_platform.eww

Please note that the projects, having their name ending with “_smp” are meant for the execution on the

RZ/N1D. SMP stands for Synchronous Multiprocessing and it matches the architecture of the dual-core Cortex

A7 of RZ/N1D. Nevertheless, you can also run the non-smp projects on RZ/N1D, however smp projects will

not run on the RZ/N1S, since RZ/N1S contains a single-core Cortex A7.

5. After opening the workspace, choose one of the projects in the workspace as shown below. Choose

demo_threadx project as an example.

Loading...

Loading...