HT-DV40H

8 – 39

IC11 VHILC750512-1 : AUDIO ENHANCER ( LC750512 ) ( 2/2 )

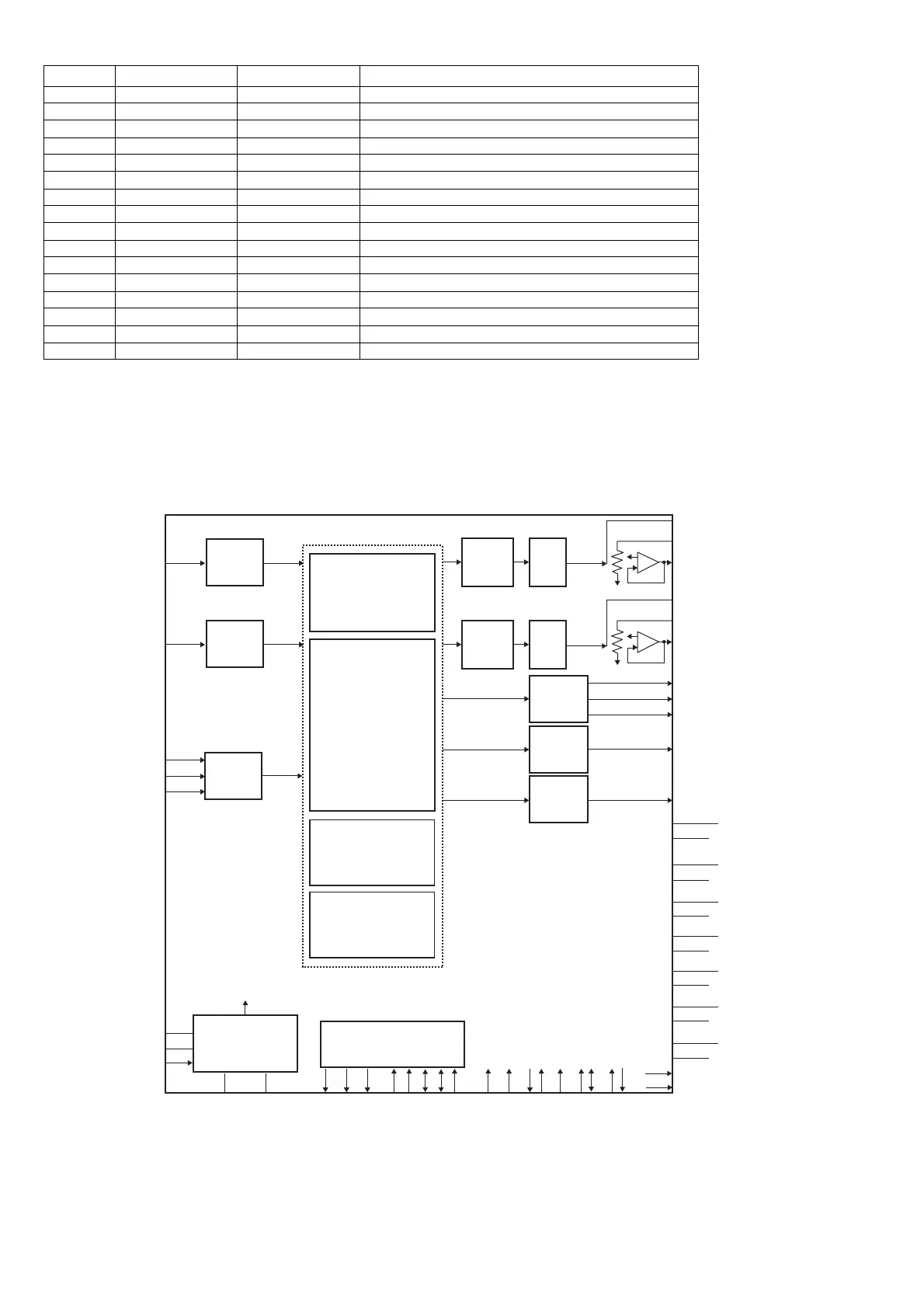

BLOCK DIAGRAM

Figure 8-7 BLOCK DIAGRAM OF IC

65 DVDD2 Input Digital power supply (+1.8V).

66 PWDB Input Power down input (L-Active).

67 RSTB Input Reset input (L-Active).

68 INTB Input Interrupt input (“H” Fixed input).

69 MCUIFSEL Input Microprocessor I/F (CCB: Low; I2C: High). Select input.

70 CE Input Microprocessor I/F chip enable.

71 SCL/CL Input Microprocessor I/F clock input.

72 I2CBUSY/DI Input/Output Microprocessor I/F data input/12CBUSY output (H-Active).

73 SDA/DO Input/Output Microprocessor I/F data input/output (Nch open drain).

74 DVSS3 — Digital GND.

75 DVDD3 Input Digital power supply (+1.8V).

76 MRREQ Output DSP-MCU communication error flag (H-Active).

77* GPFLAG Output DSP-MCU general-purpose flag (H-Active).

78* EMPF Output CCB input register status monitor flag.

79 CVSS3 — Digital GND.

80 CVDD3 Input Digital power supply (+3.3 V).

In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside.

Pin No. Terminal Name Input / Output Function

38

INR

DAOUTL

DAOUTR

EVRINL

EVRINR

AOUT1

AOUT2

LRCKO

BCKO

DATAO0

DATAO1

DATAO2

PLLAVDD

PLLAVSS

PLLDVDD

PLLDVSS

AVDD1-4

AVSS1-4

BVDD1

BVSS1

CVSS1-4

CVDD1-4

DVSS1-4

DVDD1-4

XVSS

VREF1

VREF2

XVDD

ADC

(20bit)

DSP CORE

24bit

DAC

(20bit)

L.P.F.

Program ROM

Data RAM

Delay RAM

37

INL

LRCKI

BCKI

DATAI

ADC

(20bit)

47

55

3

4

5

6

24,25,34,40

23,26,33,39

15,46,61,80

16,45,79,60

10,52,65,75

9,51,64,74

14

11

36

22

21

48

49

1

2

13

12

78

77

76

70

71

72

73

69

42,43,44

67

66

63

62

68

41

50

53

35

7,817,18,19,20,41

Audio I/F

PLLPWPR

PLLGNDR

XSEL0,1,2

XIN

XOUT

EMPF

GPFLAG

MRREQ

CE

SCL/CL

I2CBUSY/DI

SDA/DO

PWDB

PDEN

XPDESC

INTB

TEST7,5-0

TEST6

SCKI

SCKO

MCUFISEL

RSTB

PLL

VCO

CCB or I

2

C

DAC

(20bit)

Audio I/F

L.P.F.

R

56

57

58

59

32

31

30

Vref

Audio I/F

Audio I/F

R

27

28

29

Vref

Loading...

Loading...