114

LC-26GA5E

LC-32GA5E

LC-26GA5E

LC-32GA5E

Table 2 -6 provides detailed Peripheral Interface pin descriptions.

Table 2 -7

provides detailed Miscellaneous pin descriptions.

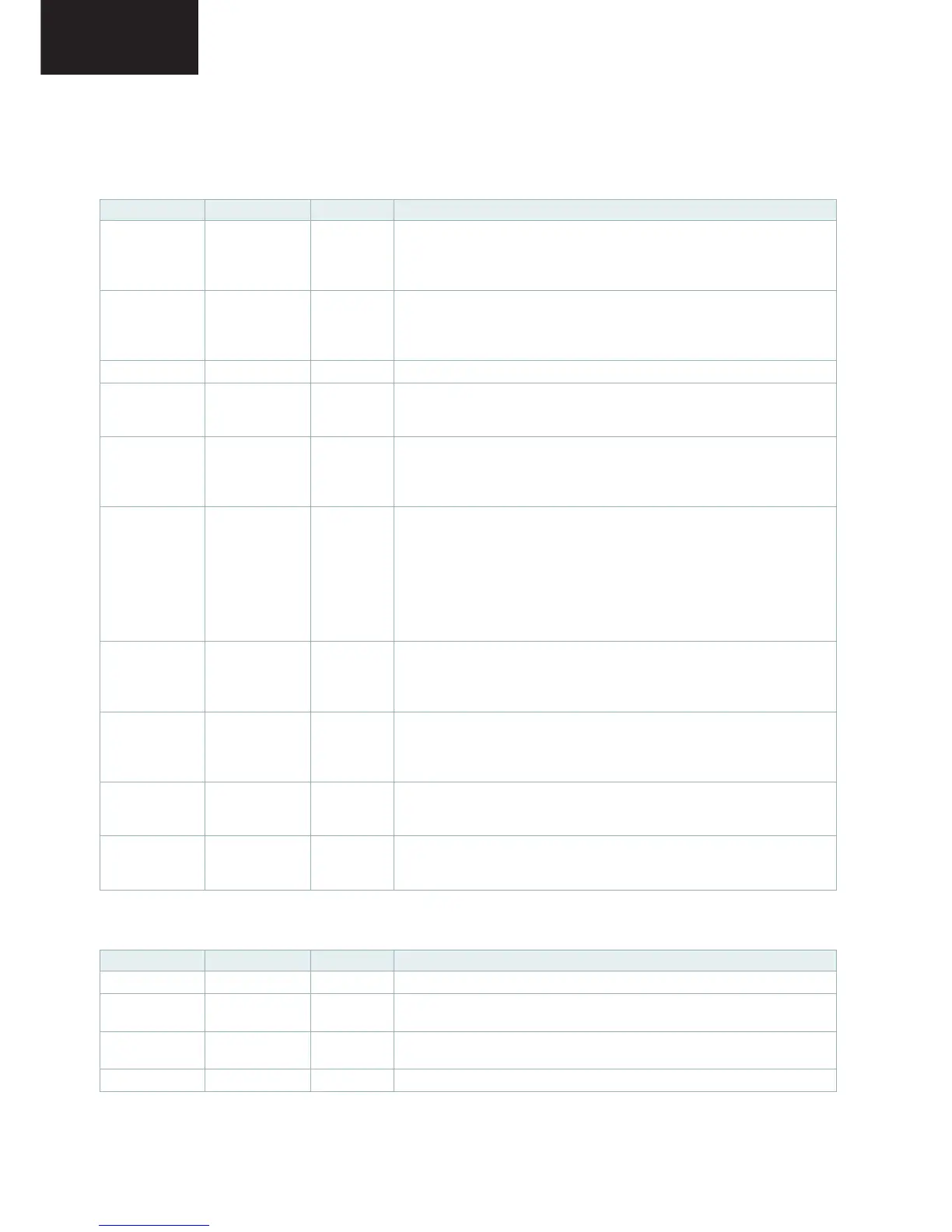

Table 2-6 Peripheral Interface Pin Descriptions

Name Pin(s) Type Function

PORTA0 208 I/O U5

General-purpose I/O port bit controlled by PADAT0 and PAEN0. This pin

has one other possible function when EXTRAMEN=1.

When EXTRAMEN=1 and PAEN0=0, PORTA1 is microprocessor address

bit 0 (A0).

PORTA1 207 I/O U5

General-purpose I/O port bit controlled by PADAT1 and PAEN1. This pin

has one other possible function when EXTRAMEN=1.

When EXTRAMEN=1 and PAEN1=0, PORTA1 is microprocessor byte-high

enable (BHEN)

PORTA2 206 I/O U5

General-purpose I/O port bit controlled by PADAT2 and PAEN2.

PORTA3 205 I/O U5

General-purpose I/O port bit controlled by PADAT3 and PAEN3. This pin

can also function as an external clock source for DCLK (DCLKEXT) when

both the internal PLLs are disabled or when DPLLBYP=1.

PORTA4 204 I/O U5

General-purpose I/O port bit controlled by PADAT4 and PAEN4. This pin

has one other possible function when IREN=1.

When IREN=1 and PAEN4=1, this pin can function as an input to the on-

chip IR receiver 0. (IRRCVR0)

PORTA5 203 I/O U5

General-purpose I/O port bit controlled by PADAT5 and PAEN5. This pin

has other possible functions depending on the IREN, EIEN registers. When

EIEN=1 and PAEN5=1, this pin can function as an external interrupt to the

on-chip CPU. When IREN=1 and PAEN5=1, this pin can function as an

input to the on-chip IR receiver 1 (IRRCVR1). When DPLLBYP=1 and

PAEN=0, this pin becomes the output of the DCLK PLL. This output can be

routed through an external spread spectrum chip and then back into port

A3 (DCLK input) to implement spread spectrum.

PORTA6 202 I/O U5

General-purpose I/O port bit controlled by PADAT6 and PAEN6. This pin

has one other possible function when PREF1EN=1.

When PREF1EN=1 and PAEN6=0, PORTA6 is a variable duty-cycle pulse

reference generator (PWM) output controlled by PREF1HI and PREF1LO.

PORTA7 201 I/O D5

General-purpose I/O port bit controlled by PADAT7 and PAEN7. This pin

has one other possible function when PREF0EN=1.

When PREF0EN=1 and PAEN7=0, PORTA7 is a variable duty-cycle pulse

reference generator (PWM) output controlled by PREF0HI and PREF0LO.

RXD 53 I/O U5

Serial Receive Data. RXD is the serial receive data for the on-chip serial

port. This pin can also function as the 2-wire master data pin when

2WMEN=16.

TXD 54 I/O U5

Serial Transmit Data. TXD is the serial transmit data for the on-chip serial

port. This pin can also function as the 2-wire master clock output pin when

2WMEN=16.

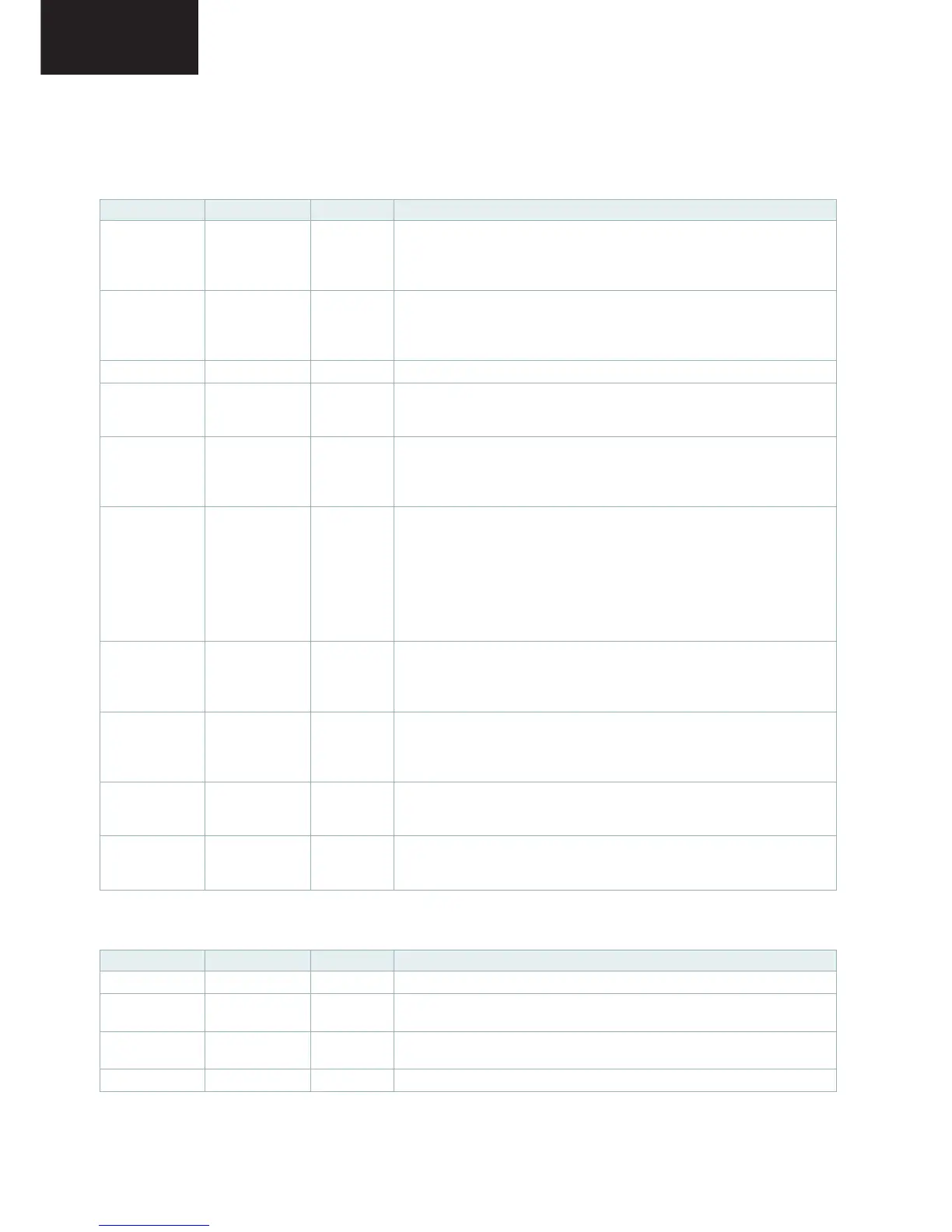

Table 2-7 Miscellaneous Pin Descriptions

Name Pin(s) Type Function

TESTEN 137 ID 5

Test Mode Enable. Connect to ground for normal operation.

RESET_N 132 BOD

Reset Output. RESET_N is a bidirectional pin that can be used to either

drive external logic in the system or receive an external reset signal.

XI 169 I

Crystal Input. Connect to external crystal. XI can also function as the MCLK

input LVTTL-level signal from an external oscillator.

XO 170 O

Crystal Output. Connect to external crystal.

3.3. Description of Pins IC2201, continued

CONFIDENTIAL

Loading...

Loading...